# 40V, 300mA, Low-Quiescent Current Adjustable Output Linear Regulator

## 1 FEATURES

- Input Voltage Range: 3 V to 40 V**

- Output Voltage Range:**

- **Fixed Option: 1.8V, 2.5V, 3.0V, 3.3V and 5.0V**

- **Adjustable Option: 1.25V to 15V**

- Very Low  $I_Q$ : 7 $\mu$ A (TYP)**

- Up to 300mA Load Current**

- Very Low Dropout: 395mV at 300mA ( $V_{OUT}=5V$ )**

- Power Good**

- Programmable Power Good Delay**

- Over Temperature Protection**

- Over Current Limit Protection**

- Short Circuit Protection is Typical 350mA**

- Output Voltage Accuracy:  $\pm 1.5\%$**

- Available in a ESOP8 Package**

## 2 APPLICATIONS

- Industrial/Automotive Applications**

- Portable/Battery-Powered Equipment**

- Ultra Low-Power Microcontrollers**

- Cellular Handsets**

- Medical Imaging**

## 3 DESCRIPTIONS

The RS3017 is a Low Dropout Linear Regulator designed by CMOS technology. Which can provide 300mA output current. The device allows input voltage as high as 40V. It is very suitable for standby microprocessor control-unit systems, especially in automotive applications. Wide input voltage can make it well withstand the impact of surge voltage and ensure the stability of output voltage.

The RS3017 provides a wide variety of fixed output-voltage options: 1.8V, 2.5V, 3.0V, 3.3V and 5.0V; Also, it provides the output-adjustable option (from 1.25V to 15V).

The regulator output current is limited internally, and the device is protected against short-circuit, over-load, and over-temperature conditions.

### Device Information <sup>(1)</sup>

| PART NUMBER | PACKAGE | BODY SIZE (NOM) |

|-------------|---------|-----------------|

| RS3017      | ESOP8   | 4.90mm×3.90mm   |

(1) For all available packages, see the orderable addendum at the next page of the data sheet.

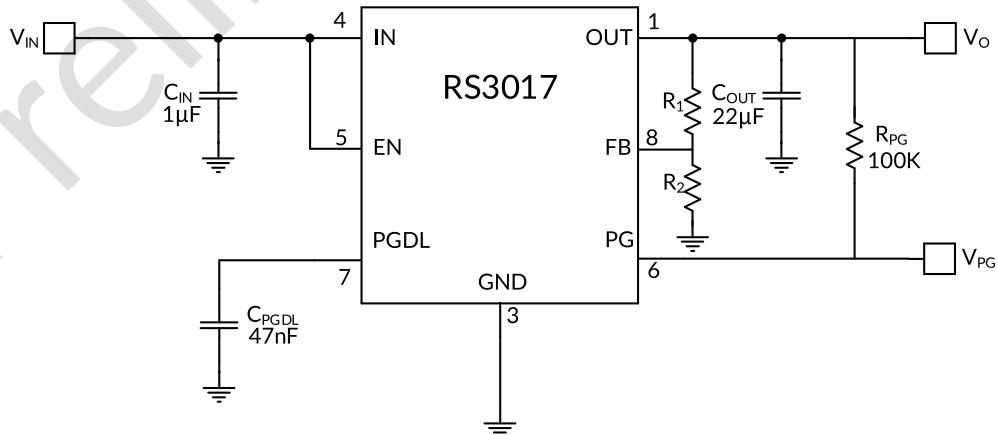

## 4 TYPICAL APPLICATION SCHEMATIC

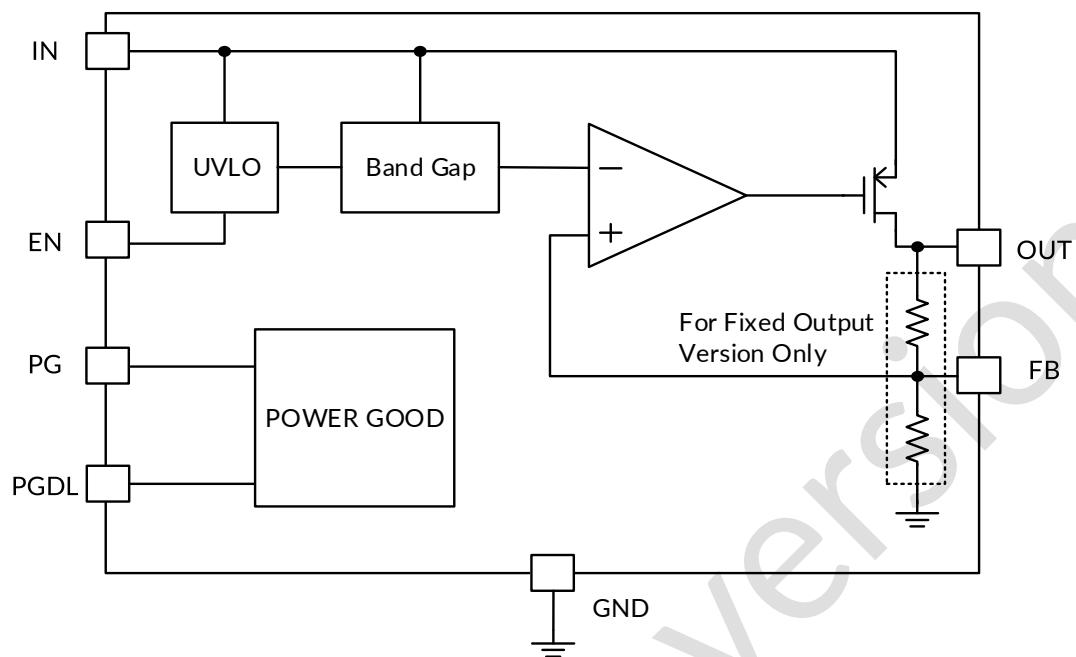

## 5 FUNCTIONAL BLOCK DIAGRAM

## Table of Contents

|                                                           |    |

|-----------------------------------------------------------|----|

| <b>1 FEATURES</b> .....                                   | 1  |

| <b>2 APPLICATIONS</b> .....                               | 1  |

| <b>3 DESCRIPTIONS</b> .....                               | 1  |

| <b>4 TYPICAL APPLICATION SCHEMATIC</b> .....              | 1  |

| <b>5 FUNCTIONAL BLOCK DIAGRAM</b> .....                   | 2  |

| <b>6 REVISION HISTORY</b> .....                           | 4  |

| <b>7 PACKAGE/ORDERING INFORMATION<sup>(1)</sup></b> ..... | 5  |

| <b>8 PIN CONFIGURATION AND FUNCTIONS</b> .....            | 6  |

| <b>9 SPECIFICATIONS</b> .....                             | 7  |

| 9.1 Absolute Maximum Ratings .....                        | 7  |

| 9.2 ESD Ratings .....                                     | 7  |

| 9.3 Recommended Operating Conditions .....                | 8  |

| 9.4 Electrical Characteristics .....                      | 9  |

| 9.5 Typical Characteristics .....                         | 11 |

| <b>10 DETAILED DESCRIPTION</b> .....                      | 20 |

| 10.1 Overview .....                                       | 20 |

| 10.2 Under Voltage Lockout (UVLO) .....                   | 20 |

| 10.3 Shutdown .....                                       | 20 |

| 10.4 Thermal Overload Protection ( $T_{SD}$ ) .....       | 20 |

| 10.5 Disabled .....                                       | 20 |

| 10.6 Current-Limit Protection .....                       | 20 |

| 10.7 Short Current-Limit Protection .....                 | 20 |

| 10.8 PG and Delay .....                                   | 20 |

| 10.9 Input and Output Capacitor Requirements .....        | 21 |

| 10.10 Adjustable Device Feedback Resistors .....          | 21 |

| <b>11 POWER SUPPLY RECOMMENDATIONS</b> .....              | 22 |

| <b>12 LAYOUT</b> .....                                    | 22 |

| <b>13 PACKAGE OUTLINE DIMENSIONS</b> .....                | 23 |

| <b>14 TAPE AND REEL INFORMATION</b> .....                 | 24 |

## **6 REVISION HISTORY**

Note: Page numbers for previous revisions may different from page numbers in the current version.

| <b>VERSION</b> | <b>Change Date</b> | <b>Change Item</b>                                                              |

|----------------|--------------------|---------------------------------------------------------------------------------|

| A.0            | 2025/07/01         | Preliminary version completed                                                   |

| A.0.1          | 2025/11/28         | 1. Update PIN CONFIGURATION AND FUNCTIONS<br>2. Update Absolute Maximum Ratings |

Preliminary Version

## 7 PACKAGE/ORDERING INFORMATION <sup>(1)</sup>

| PRODUCT     | ORDERING NUMBER  | V <sub>OUT</sub> (V) | PACKAGE LEAD | PACKAGE MARKING <sup>(2)</sup> | MSL <sup>(3)</sup> | PACKAGE OPTION      |

|-------------|------------------|----------------------|--------------|--------------------------------|--------------------|---------------------|

| RS3017-1.8  | RS3017-1.8XEK-G  | 1.8                  | ESOP8        | 3017-18                        | TBD                | Tape and Reel, 4000 |

| RS3017-2.5  | RS3017-2.5XEK-G  | 2.5                  | ESOP8        | 3017-25                        | TBD                | Tape and Reel, 4000 |

| RS3017-3.0  | RS3017-3.0XEK-G  | 3.0                  | ESOP8        | 3017-30                        | TBD                | Tape and Reel, 4000 |

| RS3017-3.3  | RS3017-3.3XEK-G  | 3.3                  | ESOP8        | 3017-33                        | TBD                | Tape and Reel, 4000 |

| RS3017-5.0  | RS3017-5.0XEK-G  | 5.0                  | ESOP8        | 3017-50                        | TBD                | Tape and Reel, 4000 |

| RS3017-ADJC | RS3017-ADJCXEK-G | ADJ                  | ESOP8        | 3017-ADJC                      | TBD                | Tape and Reel, 4000 |

NOTE:

- (1) This information is the most current data available for the designated devices. This data is subject to change without notice and revision of this document. For browser-based versions of this data sheet, refer to the right-hand navigation.

- (2) There may be additional marking, which relates to the lot trace code information (data code and vendor code), the logo or the environmental category on the device.

- (3) RUNIC classify the MSL level with using the common preconditioning setting in our assembly factory conforming to the JEDEC industrial standard J-STD-20F. Please align with RUNIC if your end application is quite critical to the preconditioning setting or if you have special requirement.

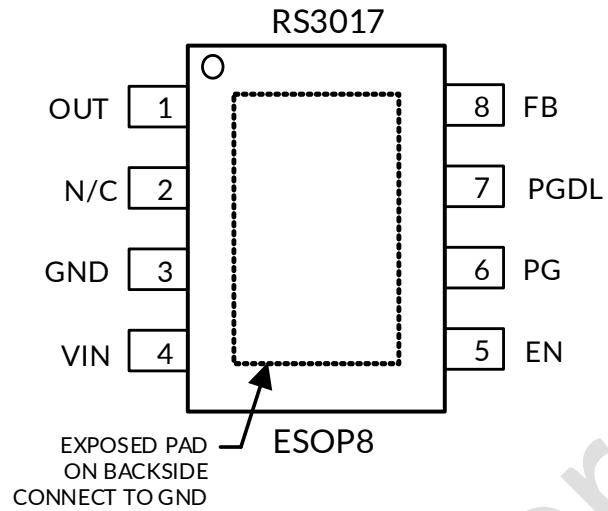

## 8 PIN CONFIGURATION AND FUNCTIONS

### PIN DESCRIPTION

| NAME | PIN   | I/O <sup>(1)</sup> | FUNCTION                                                                                                                                                               |

|------|-------|--------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|      | ESOP8 |                    |                                                                                                                                                                        |

| OUT  | 1     | O                  | Regulated output voltage.                                                                                                                                              |

| N/C  | 2     | -                  | Not-connected pin.                                                                                                                                                     |

| GND  | 3     | G                  | Ground reference.                                                                                                                                                      |

| VIN  | 4     | I                  | Input power-supply voltage.                                                                                                                                            |

| EN   | 5     | I                  | Enable pin. The device enters the standby state when the enable pin becomes lower than the enable threshold.                                                           |

| PG   | 6     | O                  | Power good. This open-drain pin must connect to $V_{OUT}$ via an external resistor. $V_{PG}$ is logic level high when $V_{OUT}$ is above the power-on-reset threshold. |

| PGDL | 7     | O                  | Power good delay adjustment. Connecting a capacitor from this pin to GND changes the PG reset delay.                                                                   |

| FB   | 8     | I                  | Feedback pin when using external resistor divider.                                                                                                                     |

(1) I = Input, O = Output, G=Ground.

## 9 SPECIFICATIONS

### 9.1 Absolute Maximum Ratings

over operating free-air temperature range (unless otherwise noted) <sup>(1)(2)</sup>

|               |                                                           | MIN                | MAX | UNIT |

|---------------|-----------------------------------------------------------|--------------------|-----|------|

| $V_{IN}$      | Input voltage                                             | -0.3               | 45  | V    |

| $V_{EN}$      | $V_{EN}$ voltage range                                    | -0.3               | 45  | V    |

| $V_{OUT}$     | $V_{OUT}$ voltage range                                   | -0.3               | 20  | V    |

| $V_{PG}$      | $V_{PG}$ voltage range                                    | -0.3               | 20  | V    |

| $V_{PGDL}$    | $V_{PGDL}$ voltage range                                  | -0.3               | 6.6 | V    |

| $V_{FB}$      | $V_{FB}$ voltage range                                    | -0.3               | 6.6 | V    |

| $T_J$         | PN Junction temperature <sup>(3)</sup>                    | -40                | 150 | °C   |

| $P_D$         | Continuous power dissipation <sup>(4)</sup>               | Internally limited |     | W    |

| $\theta_{JA}$ | Junction-to-ambient thermal resistance <sup>(5)</sup>     | ESOP8              | 30  | °C/W |

| $\theta_{JC}$ | Junction-to-case thermal resistance <sup>(5)</sup>        |                    | 20  | °C/W |

| $\Psi_{JT}$   | Junction-to-top characterization parameter <sup>(5)</sup> |                    | 10  | °C/W |

| $T_{stg}$     | Storage temperature range                                 | -40                | 150 | °C   |

- (1) Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Conditions is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

- (2) All voltages are with respect to the GND pin.

- (3) The maximum power dissipation is a function of  $T_{J(MAX)}$ ,  $R_{\theta JA}$ , and  $T_A$ . The maximum allowable power dissipation at any ambient temperature is  $P_D = (T_{J(MAX)} - T_A) / R_{\theta JA}$ . All numbers apply for packages soldered directly onto a PCB.

- (4) Internal thermal shutdown circuitry protects the device from permanent damage. The actual chip output current is subject to the input-output voltage difference, ambient temperature and PCB heat dissipation design.

- (5) The package thermal impedance is calculated in accordance with JESD-51.

### 9.2 ESD Ratings

The following ESD information is provided for handling of ESD-sensitive devices in an ESD protected area only.

|             |                                                        | VALUE | UNIT |

|-------------|--------------------------------------------------------|-------|------|

| $V_{(ESD)}$ | Human-Body Model (HBM), MIL-STD 883J                   | ±4000 | V    |

|             | Charge-Device Model (CDM), ANSI/ESDA/JEDEC JS-002-2022 | ±1000 | V    |

|             | Machine Model (MM), JESD22-A115C (2010)                | ±100  | V    |

#### ESD SENSITIVITY CAUTION

ESD damage can range from subtle performance degradation to complete device failure. Precision integrated circuits may be more susceptible to damage because very small parametric changes could cause the device not to meet its published specifications.

### 9.3 Recommended Operating Conditions

over operating free-air temperature range (unless otherwise noted)

|           |                            | MIN  | MAX | UNIT    |

|-----------|----------------------------|------|-----|---------|

| $V_{IN}$  | Input Voltage Range        | 3    | 40  | V       |

| EN        | Voltage Range of EN Pin    | 0    | 40  | V       |

| $V_{OUT}$ | Output Voltage Range       | 1.25 | 15  | V       |

| PG        | Voltage Range of PG Pin    | 0    | 15  | V       |

| $I_{OUT}$ | Output Current Range       | 1    | 300 | mA      |

| $C_{OUT}$ | Capacitor of $V_{OUT}$ pin | 2.2  | 100 | $\mu$ F |

| $T_J$     | PN Junction temperature    | -40  | 150 | °C      |

(1) All voltages are with respect to the GND pin.

(2) The chip's operating temperature is determined by the junction temperature ( $T_J$ ), the relationship between  $T_A$  and  $T_J$ , please refer to the application note as below. The larger the  $T_A$ , the smaller the space left for the chip temperature rise.

## 9.4 Electrical Characteristics

Over operating temperature range ( $-40^{\circ}\text{C} \leq T_J \leq 150^{\circ}\text{C}$ ),  $V_{\text{IN}} = 14\text{V}$ ,  $I_{\text{OUT}} = 1\text{mA}$ ,  $C_{\text{OUT}} = 22\mu\text{F}$ ,  $C_{\text{PGDL}} = 47\text{nF}$ , unless otherwise noted. Typical values are at  $T_A = 25^{\circ}\text{C}$ .

| PARAMETER                                             | SYMBOL                                                           | CONDITIONS                                                                                                                                                                                                                                                          | MIN <sup>(2)</sup>                                                                | TYP <sup>(3)</sup> | MAX <sup>(2)</sup> | UNIT                       |

|-------------------------------------------------------|------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------|--------------------|--------------------|----------------------------|

| <b>POWER SUPPLY AND CURRENTS</b>                      |                                                                  |                                                                                                                                                                                                                                                                     |                                                                                   |                    |                    |                            |

| Input Voltage <sup>(1)</sup>                          | $V_{\text{IN}}$                                                  |                                                                                                                                                                                                                                                                     | 3                                                                                 |                    | 40                 | V                          |

| Under Voltage Lockout                                 | UVLO                                                             | $V_{\text{IN}}$ rising                                                                                                                                                                                                                                              |                                                                                   | 2.6                |                    | V                          |

| Hysteresis                                            | $V_{\text{HYS}}$                                                 | $V_{\text{IN}}$ falling                                                                                                                                                                                                                                             |                                                                                   | 250                |                    | mV                         |

| Quiescent Current                                     | $I_Q$                                                            | $V_{\text{IN}} = 14\text{V}$ , $I_{\text{OUT}} = 0\text{mA}$<br>(Adjustable, $V_{\text{OUT}} = \text{FB}$ )<br>$V_{\text{IN}} = 40\text{V}$ , $I_{\text{OUT}} = 0\text{mA}$<br>(Adjustable, $V_{\text{OUT}} = \text{FB}$ )                                          |                                                                                   | 7                  |                    | $\mu\text{A}$              |

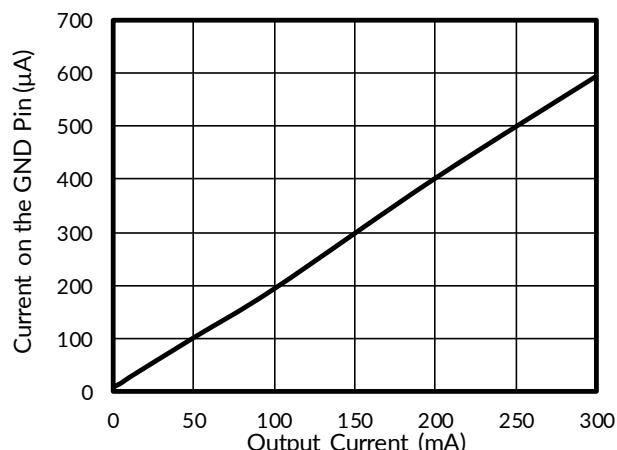

| Ground Pin Current                                    | $I_{\text{GND}}$                                                 | $I_{\text{OUT}} = 300\text{mA}$                                                                                                                                                                                                                                     |                                                                                   | 0.6                |                    | mA                         |

| Shutdown Current                                      | $I_{\text{SD}}$                                                  | $V_{\text{EN}} = 0\text{V}$ , $V_{\text{IN}} = 40\text{V}$                                                                                                                                                                                                          |                                                                                   | 1                  |                    | $\mu\text{A}$              |

| <b>OUTPUT VOLTAGE</b>                                 |                                                                  |                                                                                                                                                                                                                                                                     |                                                                                   |                    |                    |                            |

| Output Voltage Range                                  | $V_{\text{OUT}}$                                                 | Adjustable Version                                                                                                                                                                                                                                                  | $V_{\text{FB}}$                                                                   |                    | 15                 | V                          |

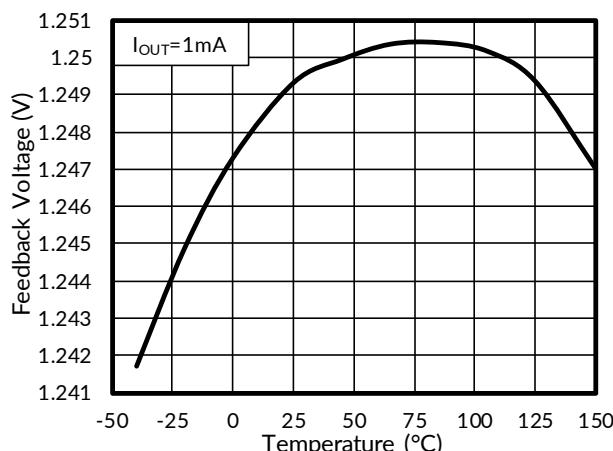

| Feedback Voltage <sup>(1)</sup>                       | $V_{\text{FB}}$                                                  | Adjustable Version, $T_J = 25^{\circ}\text{C}$ ,<br>$I_{\text{OUT}} = 1\text{mA}$                                                                                                                                                                                   | 1.2315                                                                            | 1.250              | 1.2685             | V                          |

| Feedback Pin Current                                  | $I_{\text{FB}}$                                                  | Adjustable Version, $V_{\text{FB}} = 1.3\text{V}$                                                                                                                                                                                                                   |                                                                                   |                    | 0.05               | $\mu\text{A}$              |

| DC Output Accuracy <sup>(1)</sup>                     | $\Delta V_{\text{OUT}}$                                          | $T_J = 25^{\circ}\text{C}$ , $I_{\text{OUT}} = 1\text{mA}$                                                                                                                                                                                                          |                                                                                   | $\pm 1.5$          |                    | %                          |

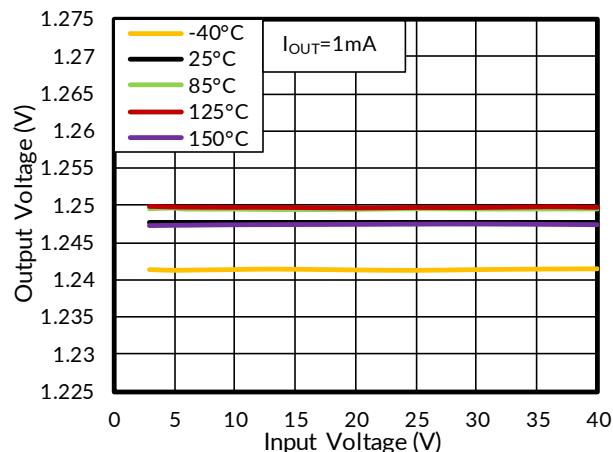

| Line Regulation <sup>(1)</sup>                        | $\Delta V_{\text{OUT}(\Delta \text{VIN})}$                       | Adjustable Version, $V_{\text{OUT}} = \text{FB}$ ; $V_{\text{IN}} = 3\text{V}$ to $40\text{V}$ , $I_{\text{OUT}} = 1\text{mA}$                                                                                                                                      |                                                                                   | 0.001              |                    | %/V                        |

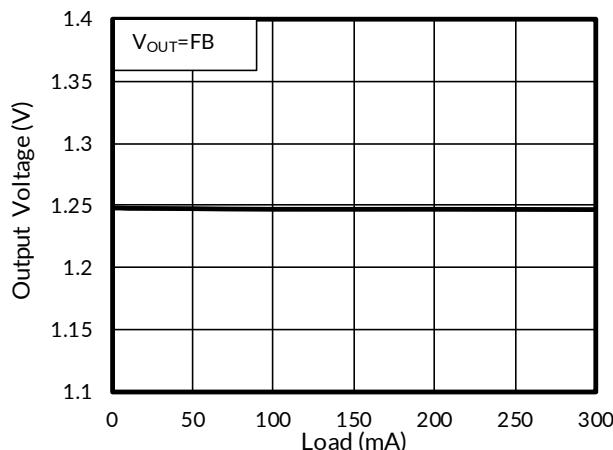

| Load Regulation <sup>(1)</sup>                        | $\Delta V_{\text{OUT}(\Delta \text{IOUT})}$                      | Adjustable Version, $V_{\text{OUT}} = \text{FB}$ ; $I_{\text{OUT}} = 1\text{mA}$ to $300\text{mA}$                                                                                                                                                                  |                                                                                   | 1                  |                    | mV                         |

| Output Voltage Temperature Coefficient <sup>(4)</sup> | $\frac{\Delta V_{\text{OUT}}}{\Delta T_A \times V_{\text{OUT}}}$ | $I_{\text{OUT}} = 1\text{mA}$ , $T_J = -40^{\circ}\text{C} \sim 85^{\circ}\text{C}$<br>$I_{\text{OUT}} = 1\text{mA}$ , $T_J = -40^{\circ}\text{C} \sim 125^{\circ}\text{C}$<br>$I_{\text{OUT}} = 1\text{mA}$ , $T_J = -40^{\circ}\text{C} \sim 150^{\circ}\text{C}$ |                                                                                   | 50                 |                    | ppm/ $^{\circ}\text{C}$    |

| Maximum Output Current <sup>(5)</sup>                 | $I_{\text{OUTMAX}}$                                              |                                                                                                                                                                                                                                                                     |                                                                                   | 45                 |                    |                            |

|                                                       |                                                                  |                                                                                                                                                                                                                                                                     |                                                                                   | 40                 |                    |                            |

| <b>DROPOUT VOLTAGE</b>                                |                                                                  |                                                                                                                                                                                                                                                                     |                                                                                   |                    |                    |                            |

| Dropout Voltage <sup>(6)</sup>                        | $V_{\text{DO}}$                                                  | $I_{\text{OUT}} = 300\text{mA}$                                                                                                                                                                                                                                     | $V_{\text{IN}} = 3\text{V}$ ,<br>$V_{\text{DO}} = V_{\text{IN}} - V_{\text{OUT}}$ |                    | 525                |                            |

|                                                       |                                                                  |                                                                                                                                                                                                                                                                     | $V_{\text{OUT}} = 3.3\text{V}$                                                    |                    | 460                |                            |

|                                                       |                                                                  |                                                                                                                                                                                                                                                                     | $V_{\text{OUT}} = 5.0\text{V}$                                                    |                    | 395                |                            |

| <b>POWER SUPPLY REJECTION RATIO AND NOISE</b>         |                                                                  |                                                                                                                                                                                                                                                                     |                                                                                   |                    |                    |                            |

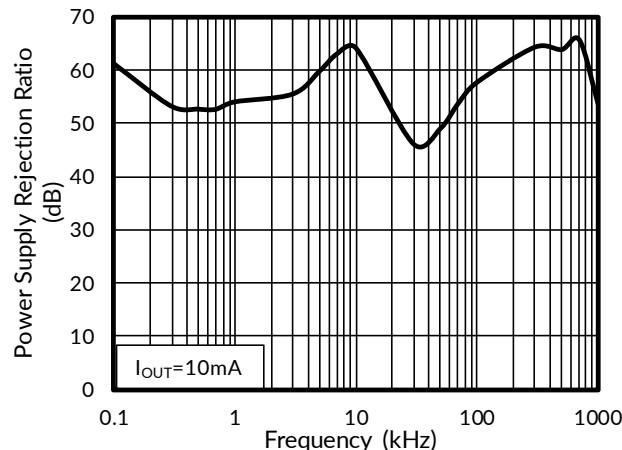

| Power Supply Rejection Ratio <sup>(7)</sup>           | PSRR                                                             | $V_{\text{IN}} = 14\text{V}$ ,<br>$V_{\text{OUT}} = 3.3\text{V}$ ,<br>$I_{\text{OUT}} = 10\text{mA}$                                                                                                                                                                | $f = 100\text{Hz}$                                                                |                    | 61                 |                            |

|                                                       |                                                                  |                                                                                                                                                                                                                                                                     | $f = 1\text{KHz}$                                                                 |                    | 53                 |                            |

|                                                       |                                                                  |                                                                                                                                                                                                                                                                     | $f = 10\text{KHz}$                                                                |                    | 64                 |                            |

|                                                       |                                                                  |                                                                                                                                                                                                                                                                     | $f = 100\text{KHz}$                                                               |                    | 57                 |                            |

| Output Noise Voltage <sup>(7)</sup>                   | $V_N$                                                            | $BW = 10\text{Hz} \sim 100\text{KHz}$ , $V_{\text{OUT}} = \text{FB}$ ,<br>$I_{\text{OUT}} = 10\text{mA}$                                                                                                                                                            |                                                                                   |                    | 80                 | $\mu\text{V}_{\text{RMS}}$ |

| <b>ENABLE AND STARTUP TIME</b>                        |                                                                  |                                                                                                                                                                                                                                                                     |                                                                                   |                    |                    |                            |

| EN Input Logic High Voltage                           | $V_{\text{IH}}$                                                  | $V_{\text{IN}} = 3\text{V}$ to $40\text{V}$ , EN rising                                                                                                                                                                                                             |                                                                                   | 1.7                |                    | V                          |

| EN Input Logic Low Voltage                            | $V_{\text{IL}}$                                                  | $V_{\text{IN}} = 3\text{V}$ to $40\text{V}$ , EN falling                                                                                                                                                                                                            |                                                                                   |                    | 0.4                | V                          |

| EN Input Leakage Current                              | $I_{\text{EN}}$                                                  | $V_{\text{IN}} = 40\text{V}$ , $V_{\text{EN}} = 0\text{V}$                                                                                                                                                                                                          |                                                                                   |                    | 0.01               | $\mu\text{A}$              |

|                                                       |                                                                  | $V_{\text{IN}} = 40\text{V}$ , $V_{\text{EN}} = 40\text{V}$                                                                                                                                                                                                         |                                                                                   |                    | 1.5                | $\mu\text{A}$              |

| Output Voltage Delay Time                             | TD                                                               | From $V_{\text{EN}} > V_{\text{IH}}$ to $V_{\text{OUT}} = 10\%$ of $V_{\text{OUT} \text{nom}}$                                                                                                                                                                      |                                                                                   |                    | 200                | $\mu\text{s}$              |

| Output Rise Time                                      | TR                                                               | From $V_{\text{OUT}} = 10\%$ to $90\%$ of $V_{\text{OUT} \text{nom}}$                                                                                                                                                                                               |                                                                                   |                    | 850                | $\mu\text{s}$              |

| <b>PG AND DELAY</b>             |                   |                                           |  |      |  |             |

|---------------------------------|-------------------|-------------------------------------------|--|------|--|-------------|

| PG Rising Threshold             | $V_{th\_PG}$      | $V_{FB}$ rising                           |  | 90%  |  | VFB         |

| PG Rising Threshold Hysteresis  | $V_{th\_PG\_hys}$ | $V_{FB}$ falling                          |  | 5.5% |  |             |

| PG Low Voltage                  | $V_{PG}$          | Sink 1mA Current                          |  | 0.1  |  | V           |

| PG Leakage Current              | $I_{PG\_LKG}$     | $V_{PG} = 5V$                             |  | 0.01 |  | $\mu A$     |

| PGDL Charging Current           | $I_{PGDL}$        | $V_{PGDL} = 1V$                           |  | 5.7  |  | $\mu A$     |

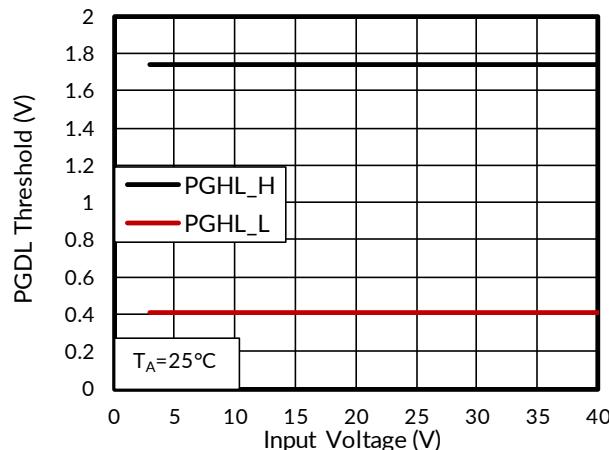

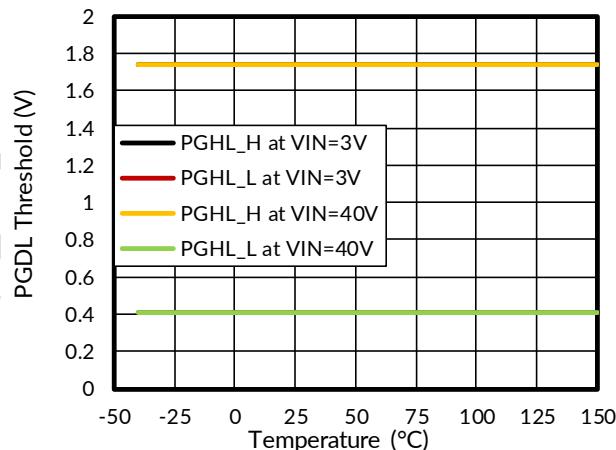

| PGDL Rising Threshold           | $PGDL\_H$         | PGDL rising                               |  | 1.74 |  | V           |

| PGDL Falling Threshold          | $PGDL\_L$         | PGDL falling                              |  | 0.4  |  | V           |

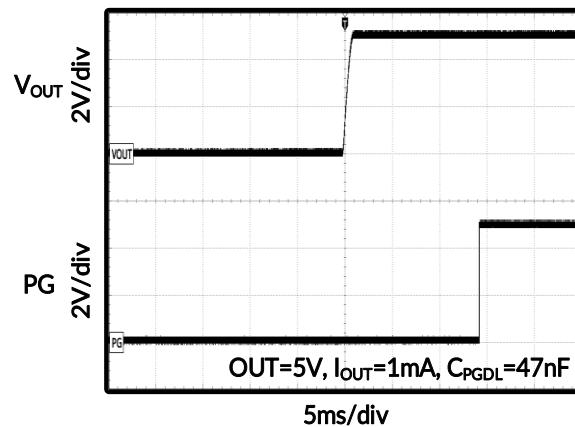

| PG Delay Time                   | $t_{PGDL}$        | $C_{PGDL} = 47nF$                         |  | 14.5 |  | ms          |

| PG Deglitch Time                | $t_{(Deglitch)}$  | $C_{PGDL} = 47nF$                         |  | 250  |  | $\mu s$     |

| <b>PROTECTIONS</b>              |                   |                                           |  |      |  |             |

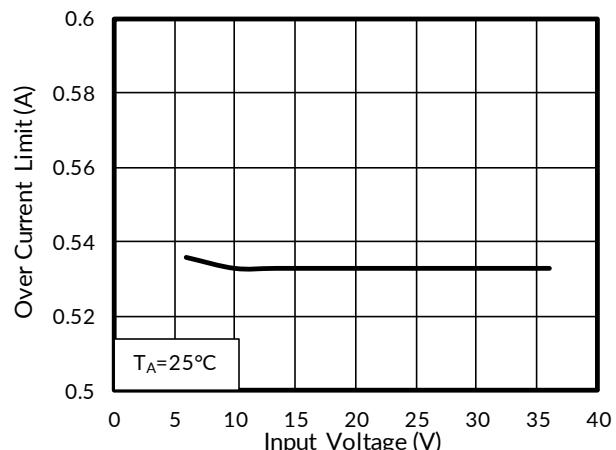

| Over Current Limit              | $I_{LMT}$         | $V_{IN} = 14V, V_{OUT} = 0.95*V_{OUTnom}$ |  | 550  |  | mA          |

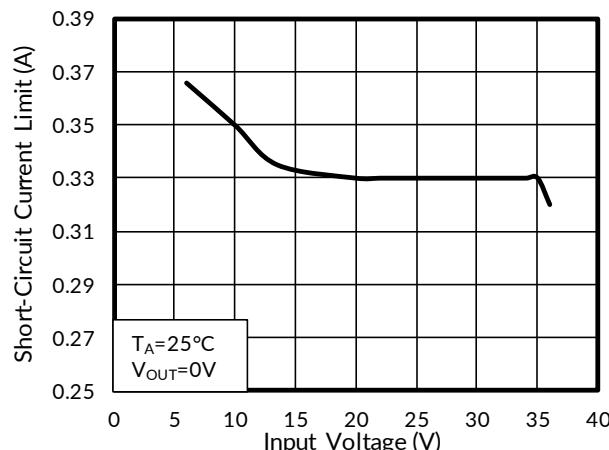

| Short-Circuit Current Limit     | $I_{SC}$          | $V_{IN} = 14V, V_{OUT} = 0V$              |  | 350  |  | mA          |

| Thermal Shutdown Threshold (7)  | $T_{TSD}$         | $T_J$ rising                              |  | 160  |  | $^{\circ}C$ |

| Thermal Shutdown Hysteresis (7) | $T_{HYS}$         | $T_J$ falling from shutdown               |  | 30   |  | $^{\circ}C$ |

**NOTE:**

- (1) Minimum  $V_{IN} = V_{OUT} + V_{DO}$  or 3V, whichever is greater.

- (2) Limits are 100% production tested at 25°C. Limits over the operating temperature range are ensured through correlations using statistical quality control (SQC) method.

- (3) Typical values represent the most likely parametric norm as determined at the time of characterization. Actual typical values may vary over time and will also depend on the application and configuration.

- (4) Output voltage temperature coefficient is defined as the worst-case voltage change divided by the total temperature range.

- (5) Maximum output current is affected by the PCB layout, size of metal trace, the thermal conduction path between metal layers, ambient temperature and the other environment factors of system. Attention should be paid to the dropout voltage when  $V_{IN} < V_{OUT} + V_{DROP}$ .

- (6) The dropout voltage is defined as  $V_{IN} - V_{OUT}$ , when  $V_{OUT}$  is 2% below the value of  $V_{OUT}$  for  $V_{IN} = V_{OUTnom} + 1V$ .

- (7) Guaranteed by design and characterization, not a FT item.

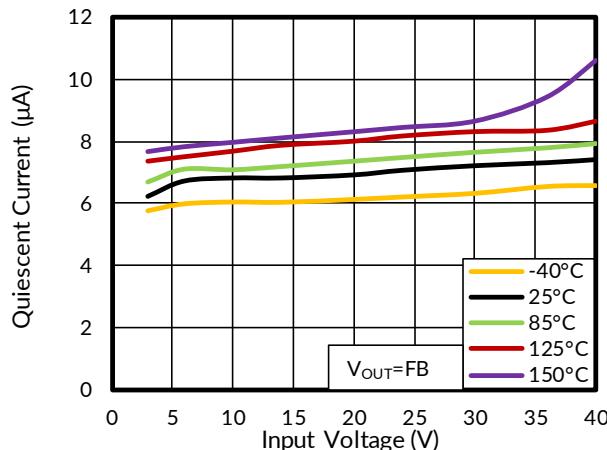

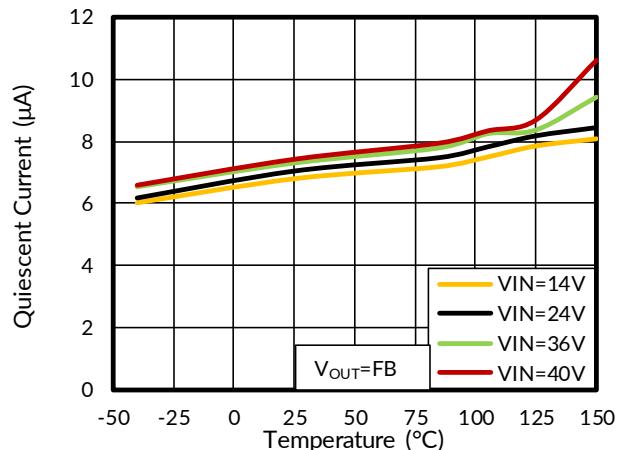

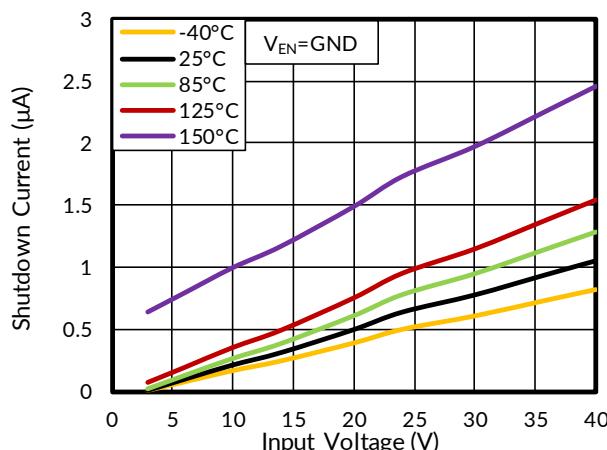

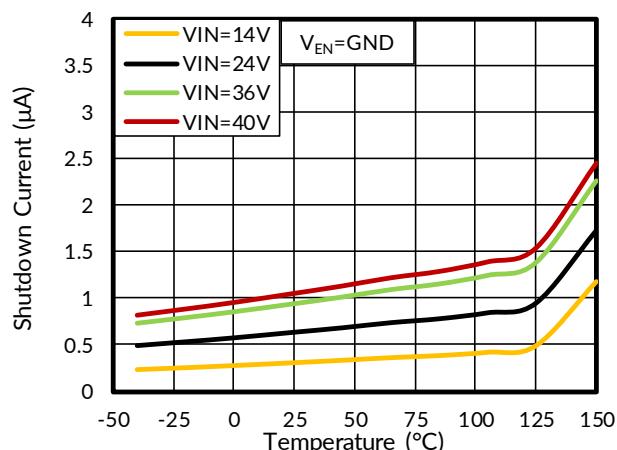

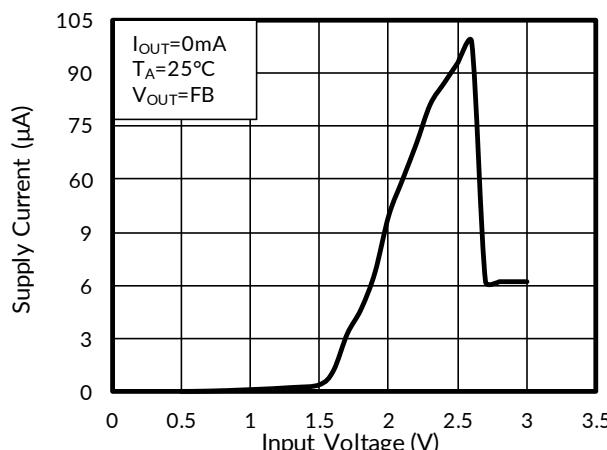

## 9.5 Typical Characteristics

NOTE: The graphs and tables provided following this note are a statistical summary based on a limited number of samples and are provided for informational purposes only.

At  $V_{IN} = 14V$ ,  $C_{IN} = 1\mu F$ ,  $C_{OUT} = 22\mu F$ ,  $C_{PGDL} = 47nF$ , unless otherwise noted.

**Figure 1. Quiescent Current vs Input Voltage**

**Figure 2. Quiescent Current vs Junction Temperature**

**Figure 3. Shutdown Current vs Input Voltage**

**Figure 4. Shutdown Current vs Junction Temperature**

**Figure 5. Supply Current vs Input Voltage**

**Figure 6. Ground Pin Current vs Output Current**

## Typical Characteristics

NOTE: The graphs and tables provided following this note are a statistical summary based on a limited number of samples and are provided for informational purposes only.

At  $V_{IN} = 14V$ ,  $C_{IN} = 1\mu F$ ,  $C_{OUT} = 22\mu F$ ,  $C_{PGDL} = 47nF$ , unless otherwise noted.

**Figure 7. Load Regulation**

**Figure 8. Line Regulation**

**Figure 9. Feedback Voltage vs Junction Temperature**

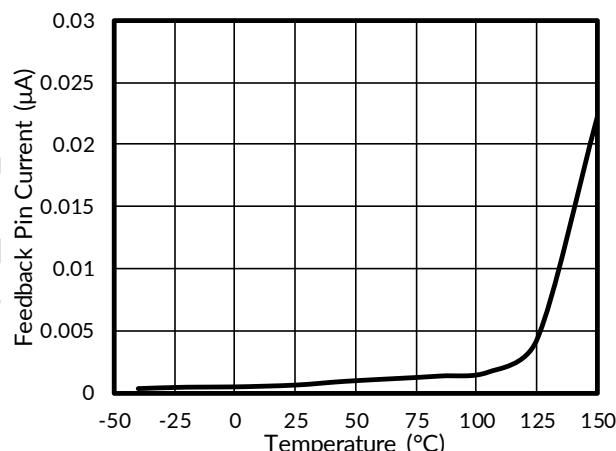

**Figure 10. Feedback Pin Current vs Junction Temperature**

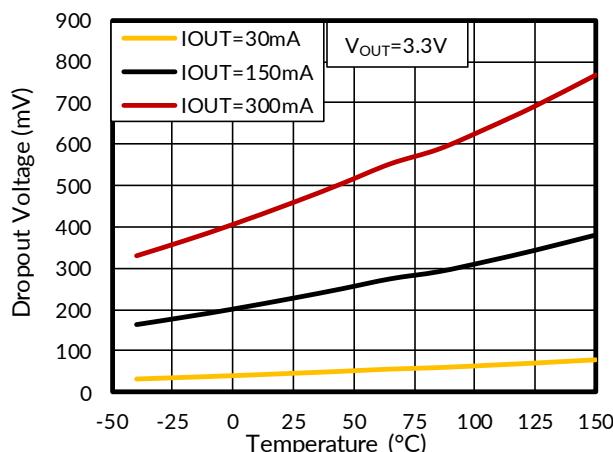

**Figure 11. Dropout Voltage vs Junction Temperature**

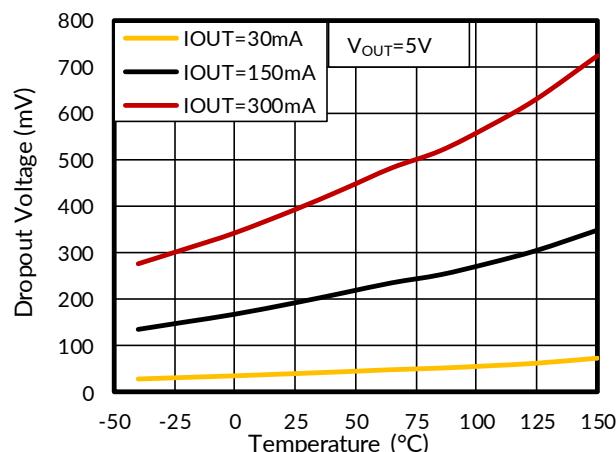

**Figure 12. Dropout Voltage vs Junction Temperature**

## Typical Characteristics

NOTE: The graphs and tables provided following this note are a statistical summary based on a limited number of samples and are provided for informational purposes only.

At  $V_{IN} = 14V$ ,  $C_{IN} = 1\mu F$ ,  $C_{OUT} = 22\mu F$ ,  $C_{PGDL} = 47nF$ , unless otherwise noted.

**Figure 13. Power Supply Rejection Ratio vs Frequency**

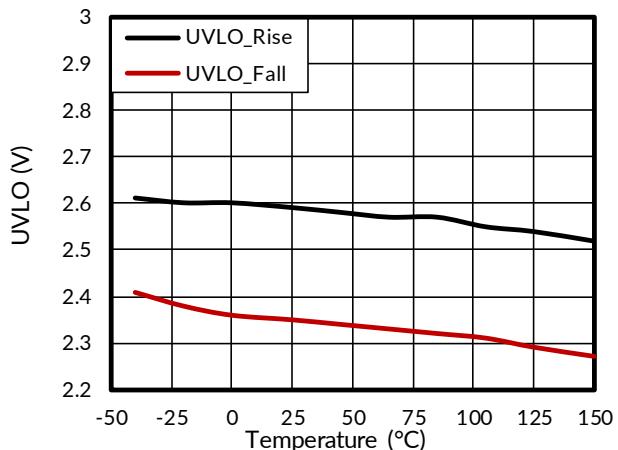

**Figure 14. UVLO vs Junction Temperature**

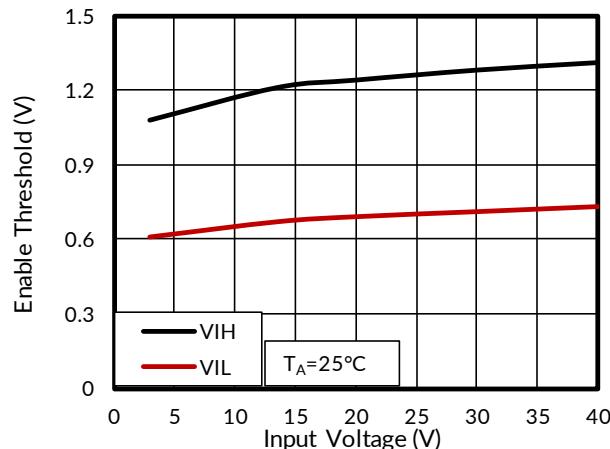

**Figure 15. Enable Threshold vs Input Voltage**

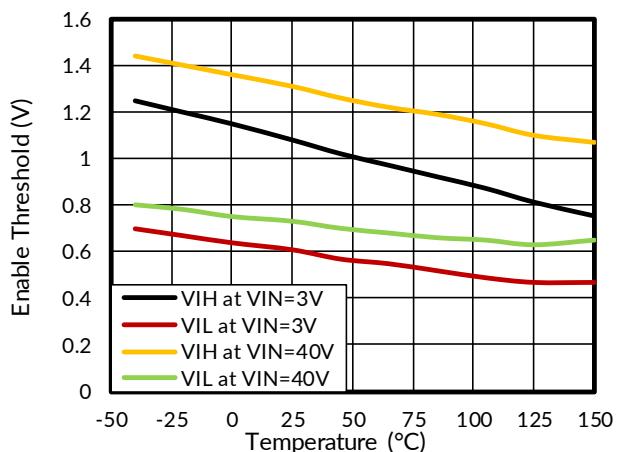

**Figure 16. Enable Threshold vs Junction Temperature**

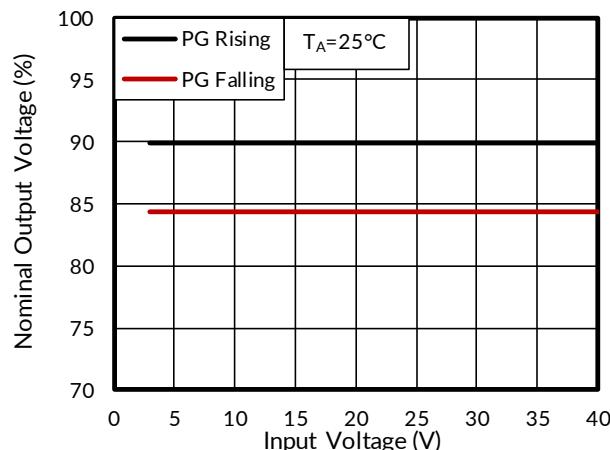

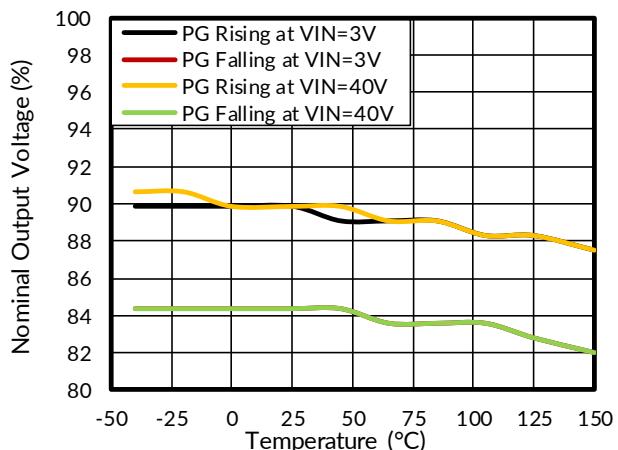

**Figure 17. Power-Good Threshold Voltage vs Input Voltage**

**Figure 18. Power-Good Threshold Voltage vs Junction Temperature**

## Typical Characteristics

NOTE: The graphs and tables provided following this note are a statistical summary based on a limited number of samples and are provided for informational purposes only.

At  $V_{IN} = 14V$ ,  $C_{IN} = 1\mu F$ ,  $C_{OUT} = 22\mu F$ ,  $C_{PGDL} = 47nF$ , unless otherwise noted.

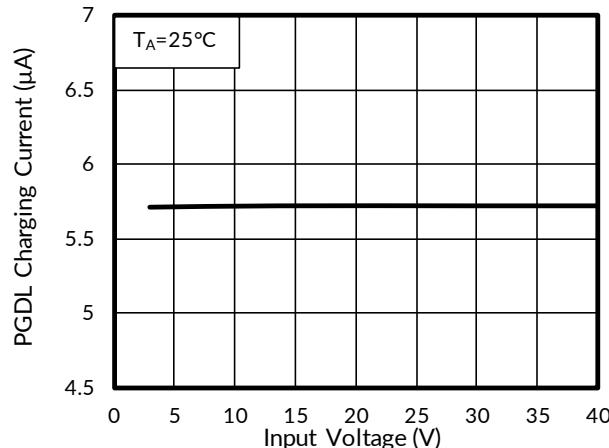

**Figure 19. PGDL Charging Current ( $V_{PGDL} = 1V$ )**

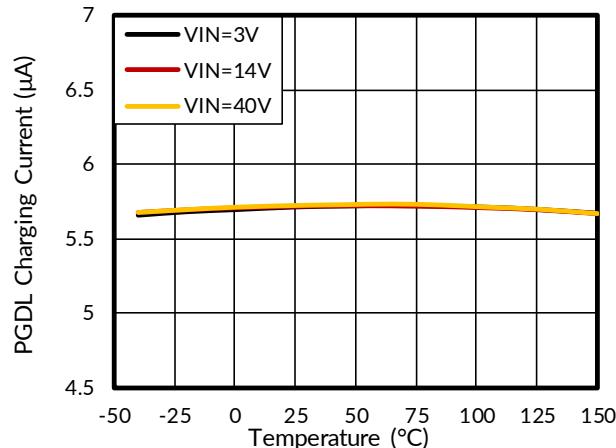

**Figure 20. PGDL Charging Current ( $V_{PGDL} = 1V$ )**

**Figure 21. PGDL Charging Threshold**

**Figure 22. PGDL Charging Threshold**

**Figure 23. Short-Circuit Current Limit vs Input Voltage**

**Figure 24. Over Current Limit vs Input Voltage**

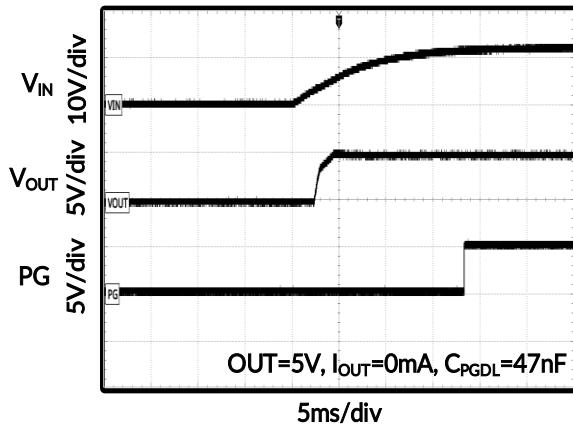

## Typical Characteristics

NOTE: The graphs and tables provided following this note are a statistical summary based on a limited number of samples and are provided for informational purposes only.

At  $V_{IN} = 14V$ ,  $C_{IN} = 1\mu F$ ,  $C_{OUT} = 22\mu F$ ,  $C_{PGDL} = 47nF$ , unless otherwise noted.

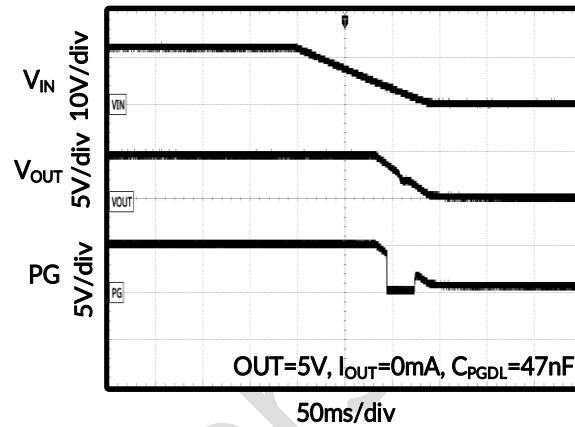

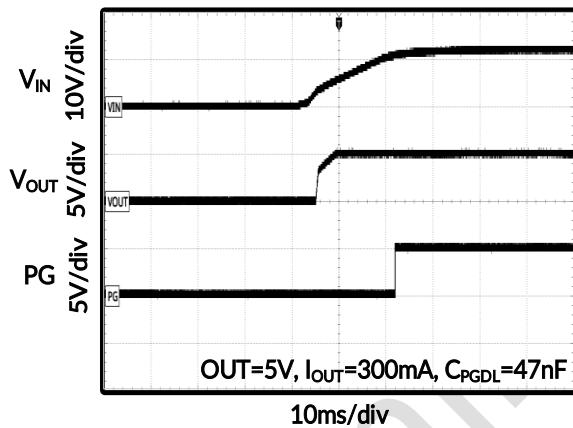

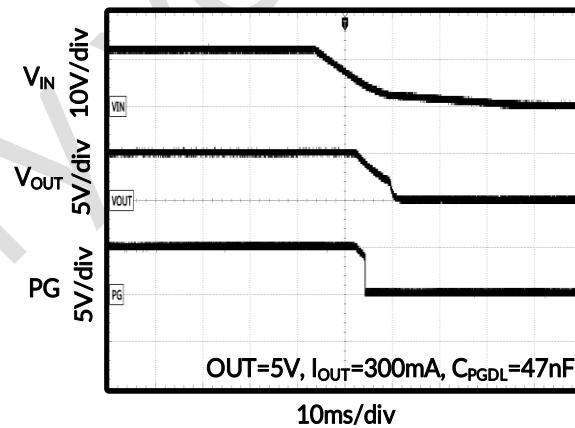

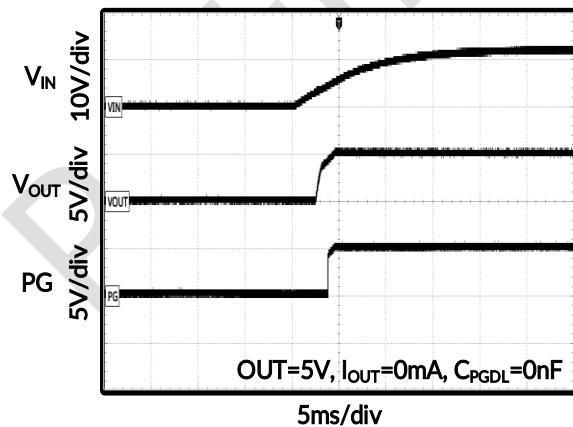

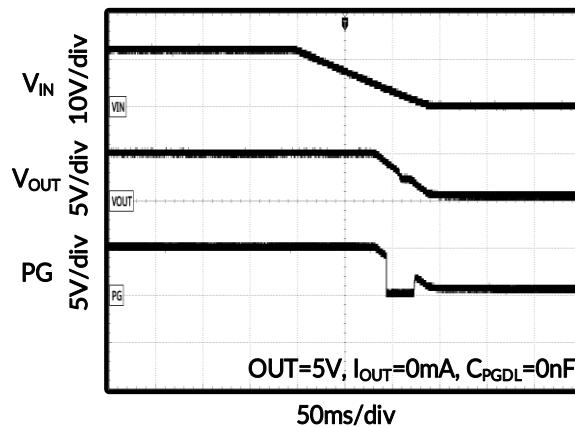

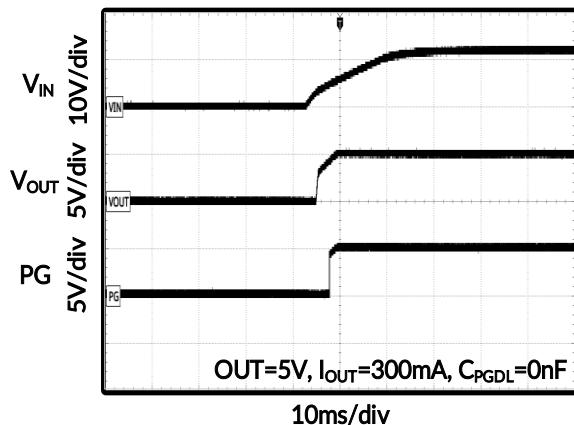

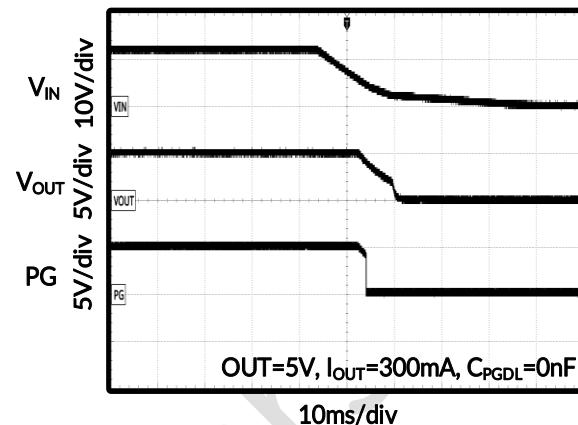

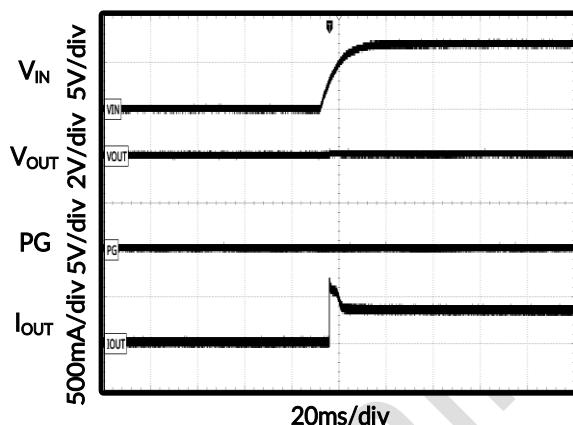

**Figure 25. Start-Up Through  $V_{IN}$**

**Figure 26. Start-Up Through  $V_{IN}$**

**Figure 27. Start-Up Through  $V_{IN}$**

**Figure 28. Start-Up Through  $V_{IN}$**

**Figure 29. Start-Up Through  $V_{IN}$**

**Figure 30. Start-Up Through  $V_{IN}$**

## Typical Characteristics

NOTE: The graphs and tables provided following this note are a statistical summary based on a limited number of samples and are provided for informational purposes only.

At  $V_{IN} = 14V$ ,  $C_{IN} = 1\mu F$ ,  $C_{OUT} = 22\mu F$ ,  $C_{PGDL} = 47nF$ , unless otherwise noted.

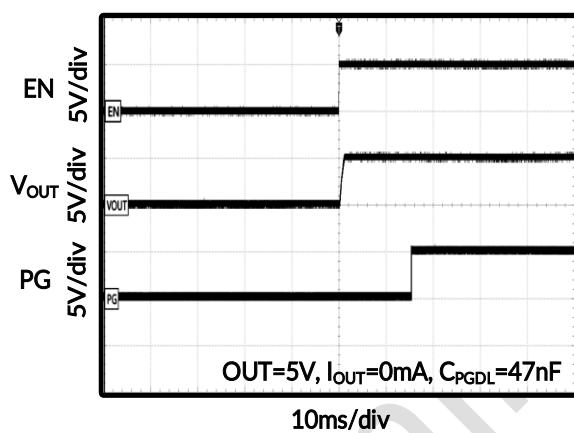

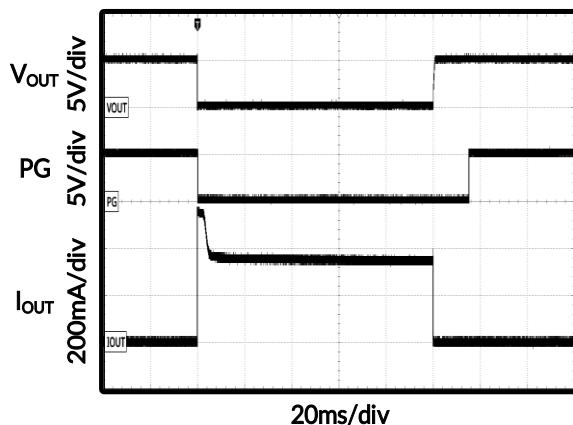

**Figure 31. Start-Up Through  $V_{IN}$**

**Figure 32. Start-Up Through  $V_{IN}$**

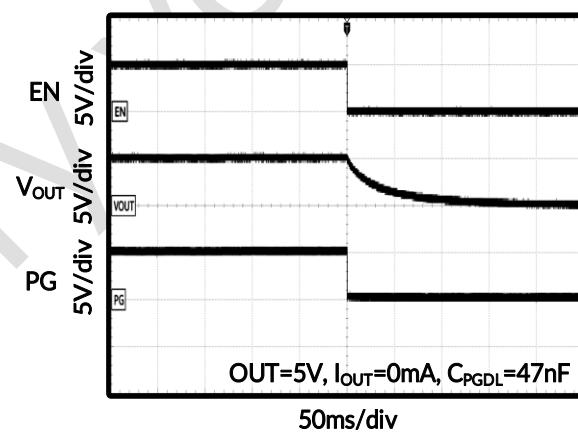

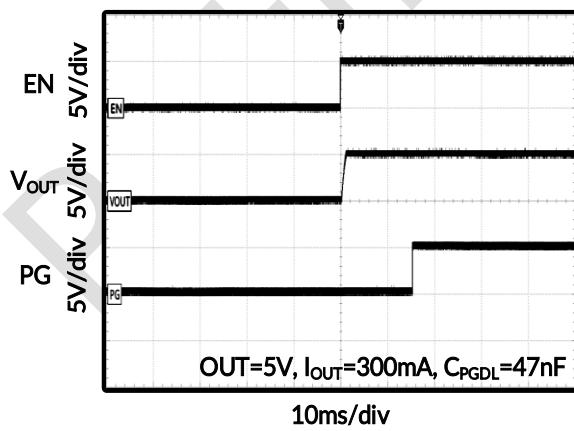

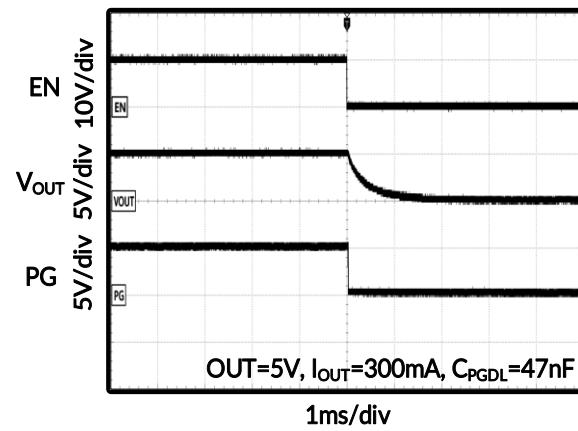

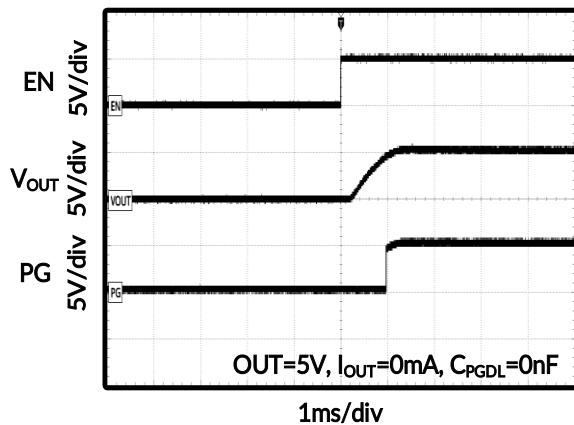

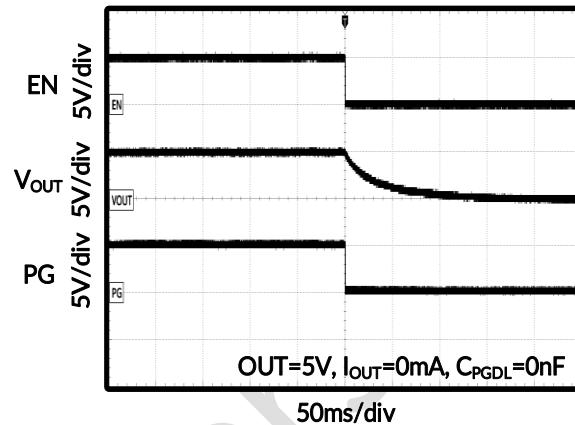

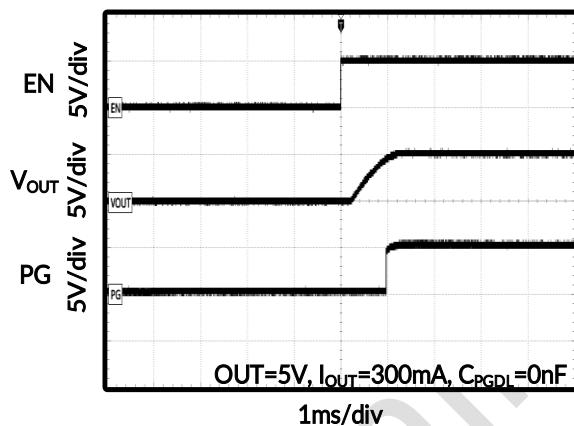

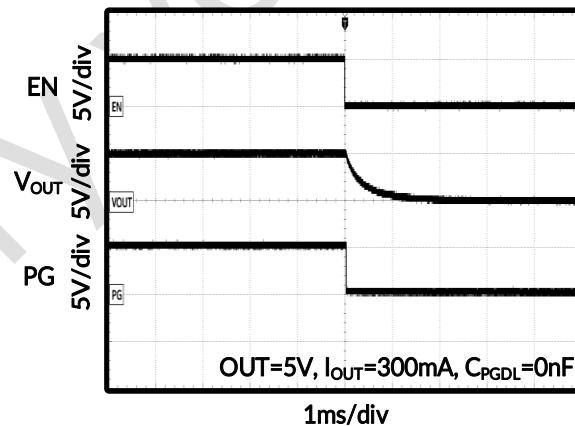

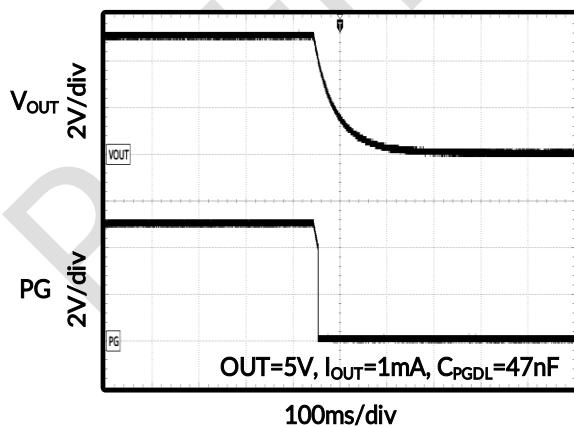

**Figure 33. Start-Up Through  $EN$**

**Figure 34. Start-Up Through  $EN$**

**Figure 35. Start-Up Through  $EN$**

**Figure 36. Start-Up Through  $EN$**

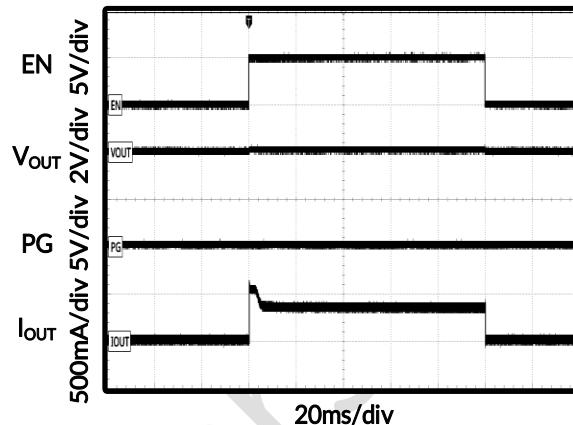

## Typical Characteristics

NOTE: The graphs and tables provided following this note are a statistical summary based on a limited number of samples and are provided for informational purposes only.

At  $V_{IN} = 14V$ ,  $C_{IN} = 1\mu F$ ,  $C_{OUT} = 22\mu F$ ,  $C_{PGDL} = 47nF$ , unless otherwise noted.

Figure 37. Start-Up Through EN

Figure 38. Start-Up Through EN

Figure 39. Start-Up Through EN

Figure 40. Start-Up Through EN

Figure 41. Over-Temperature Protection

Figure 42. Over-Temperature Protection

## Typical Characteristics

NOTE: The graphs and tables provided following this note are a statistical summary based on a limited number of samples and are provided for informational purposes only.

At  $V_{IN} = 14V$ ,  $C_{IN} = 1\mu F$ ,  $C_{OUT} = 22\mu F$ ,  $C_{PGDL} = 47nF$ , unless otherwise noted.

**Figure 43. Turn On First, Then Short Circuit**

**Figure 44. Short Circuit First, Then EN Power ON**

**Figure 45. Short Circuit First, Then VIN Power ON**

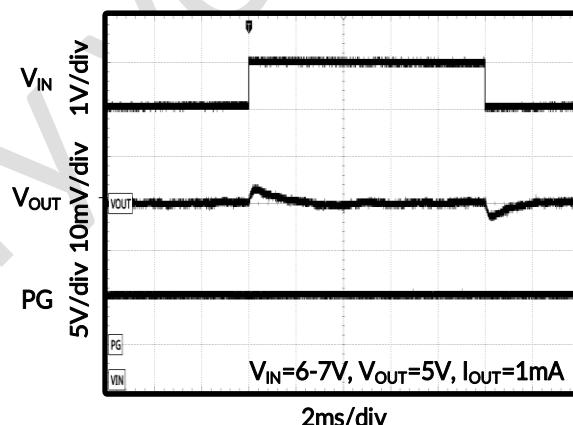

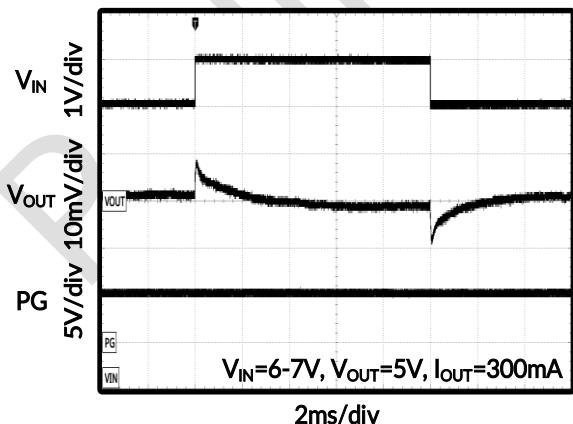

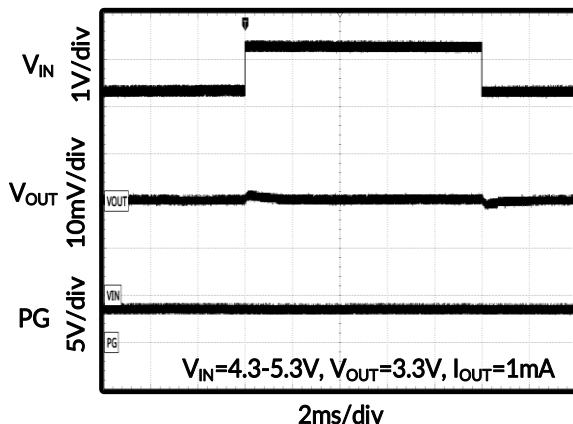

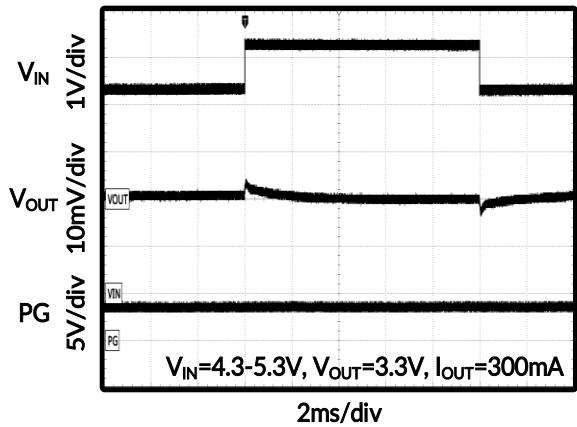

**Figure 46. Line Transient Response**

**Figure 47. Line Transient Response**

**Figure 48. Line Transient Response**

## Typical Characteristics

NOTE: The graphs and tables provided following this note are a statistical summary based on a limited number of samples and are provided for informational purposes only.

At  $V_{IN} = 14V$ ,  $C_{IN} = 1\mu F$ ,  $C_{OUT} = 22\mu F$ ,  $C_{PGDL} = 47nF$ , unless otherwise noted.

**Figure 49. Line Transient Response**

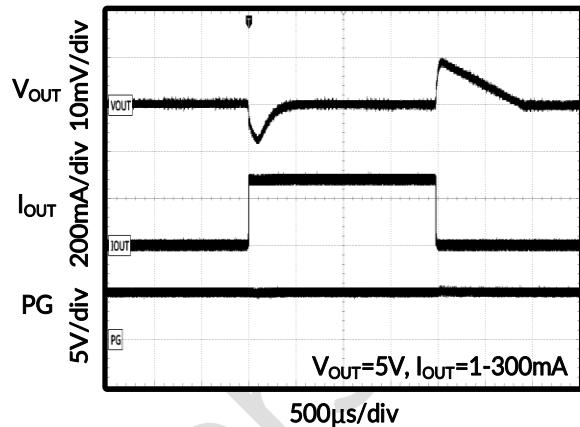

**Figure 50. Load Transient Response**

**Figure 51. Load Transient Response**

## 10 DETAILED DESCRIPTION

### 10.1 Overview

The RS3017 is a Low Dropout Linear Regulator designed by CMOS technology. Which can provide 300mA output current. The device allows input voltage as high as 40V. It is very suitable for standby microprocessor control-unit systems, especially in automotive applications. Wide input voltage can make it well withstand the impact of surge voltage and ensure the stability of output voltage.

The RS3017 provides a wide variety of fixed output-voltage options: 1.8V, 2.5V, 3.0V, 3.3V and 5.0V; Also, it provides the output-adjustable option (from 1.25V to 15V).

The regulator output current is limited internally, and the device is protected against short-circuit, over-load, and over-temperature conditions.

### 10.2 Under Voltage Lockout (UVLO)

The RS3017 family of devices uses an under voltage lockout circuit to keep the output shut off until the internal circuitry is operating properly.

### 10.3 Shutdown

Enable input. A low voltage ( $< V_{IL}$ ) on this pin turns the regulator off and a high voltage ( $> V_{IH}$ ) on this pin enables the regulator output. The EN pin can be connected to the VIN pin if not used. Do not leave floating.

### 10.4 Thermal Overload Protection ( $T_{SD}$ )

Thermal shutdown disables the output when the junction temperature rises to approximately 160°C which allows the device to cool. When the junction temperature cools to approximately 130°C, the output circuitry enables.

Based on power dissipation, thermal resistance, and ambient temperature, the thermal protection circuit may cycle on and off. This thermal cycling limits the dissipation of the regulator and protects it from damage as a result of overheating.

The thermal shutdown circuitry of the RS3017 has been designed to protect against temporary thermal overload conditions. The  $T_{SD}$  circuitry was not intended to replace proper heat-sinking. Continuously running the RS3017 device into thermal shutdown may degrade device reliability.

### 10.5 Disabled

The device is disabled under the following conditions:

- The input voltage is less than the UVLO threshold minus  $V_{HYS}$ , or has not yet exceeded the UVLO threshold.

- The enable voltage is less than the enable falling threshold voltage or has not yet exceeded the enable rising threshold.

- The device junction temperature is greater than the thermal shutdown temperature.

### 10.6 Current-Limit Protection

The RS3017 monitors the current flowing through the output PMOS and limits the maximum current to prevent damage to the load and RS3017 during current overload conditions.

### 10.7 Short Current-Limit Protection

The short current-limit function reduces the current-limit level down to 350mA (typical) during short circuit conditions.

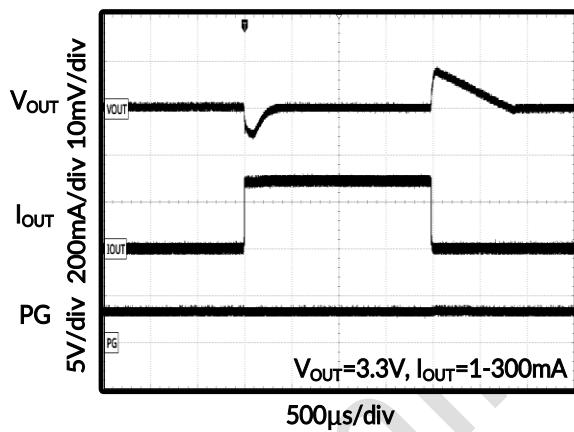

### 10.8 PG and Delay

RS3017 has one power good (PG) pin. The PG pin is the open drain of an internal MOSFET. It should be connected to  $V_{OUT}$  (<15V) through a resistor. After the  $V_{FB}$  reaches 90% of nominal value, the MOSFET turns off

and PG pin is pulled to high by  $V_{OUT}$ . When the  $V_{FB}$  drops to 84.5% of nominal value, the PG voltage is pulled to GND.

There is a delay time when PG asserts high. The delay time can be programmed by adding a capacitor on PGDL. To select a capacitor for PGDL, use below equation:

$$C_{PGDL} (\text{nF}) = \frac{t_{PGDL} (\text{ms}) \times I_{PGDL} (\mu\text{A})}{PGDL\_H (\text{V})} \quad (1)$$

Where  $t_{PGDL}$  is the desired delay time for PG asserts high,  $I_{PGDL}$  (5.7 $\mu\text{A}$ , TYP) is the PGDL charging current and  $PGDL\_H$  (1.74V, TYP) is the PGDL rising threshold.

Figure 52 shows the power good timing.

**Figure 52. Conditions for Activation of Reset**

## 10.9 Input and Output Capacitor Requirements

Connecting a 1 $\mu\text{F}$  low-equivalent series resistance (ESR) capacitor across the input supply near the regulator is good analog design practice. This capacitor counteracts reactive input sources and improves transient response and ripple rejection. A higher value capacitor can be necessary if large, fast, rise-time load transients are anticipated or if the device is located several inches from the power source.

The RS3017 family of devices is designed to be stable with standard ceramic output capacitors of values 2.2 $\mu\text{F}$  or larger. However, for better performance, 22 $\mu\text{F}$  or larger is recommended. X5R- and X7R-type capacitors are best because they have minimal variation in value and ESR over temperature.

## 10.10 Adjustable Device Feedback Resistors

The adjustable-version device requires external feedback divider resistors to set the output voltage.  $V_{OUT}$  is set using the feedback divider resistors,  $R_1$  and  $R_2$ , according to the following equation:

$$V_{OUT} = V_{FB} \times (1 + R_1 / R_2) \quad (2)$$

To ignore the FB pin current error term in the  $V_{OUT}$  equation, set the feedback divider current to 100x the FB pin current listed in the Electrical Characteristics table. This setting provides the maximum feedback divider series resistance, as shown in the following equation:

$$R_1 + R_2 \leq V_{OUT} / (I_{FB} \times 100) \quad (3)$$

## 11 POWER SUPPLY RECOMMENDATIONS

The device is designed to operate from an input voltage supply range between 3V and 40V. The input voltage range must provide adequate headroom in order for the device to have a regulated output. This input supply must be well regulated. If the input supply is noisy, additional input capacitors with low ESR can help improve output noise.

## 12 LAYOUT

For best overall performance, place all circuit components on the same side of the circuit board and as near as practical to the respective LDO pin connections. Place ground return connections to the input and output capacitor, and to the LDO ground pin as close to each other as possible, connected by a wide, component-side, copper surface. The use of vias and long traces to create LDO component connections is strongly discouraged and negatively affects system performance. This grounding and layout scheme minimizes inductive parasitics, and thereby reduces load-current transients, minimizes noise, and increases circuit stability. A ground reference plane is also recommended and is either embedded in the printed circuit board (PCB) itself or located on the bottom side of the PCB opposite the components. This reference plane serves to assure accuracy of the output voltage, shields the LDO from noise, and behaves similar to a thermal plane to spread (or sink) heat from the LDO device when connected to the exposed thermal pad. In most applications, this ground plane is necessary to meet thermal requirements.

To improve ac performance (such as PSRR, output noise, and transient response), designing the board with separate ground planes for  $V_{IN}$  and  $V_{OUT}$  is recommended, with each ground plane connected only at the GND pin of the device. In addition, the ground connection for the bypass capacitor must connect directly to the GND pin of the device.

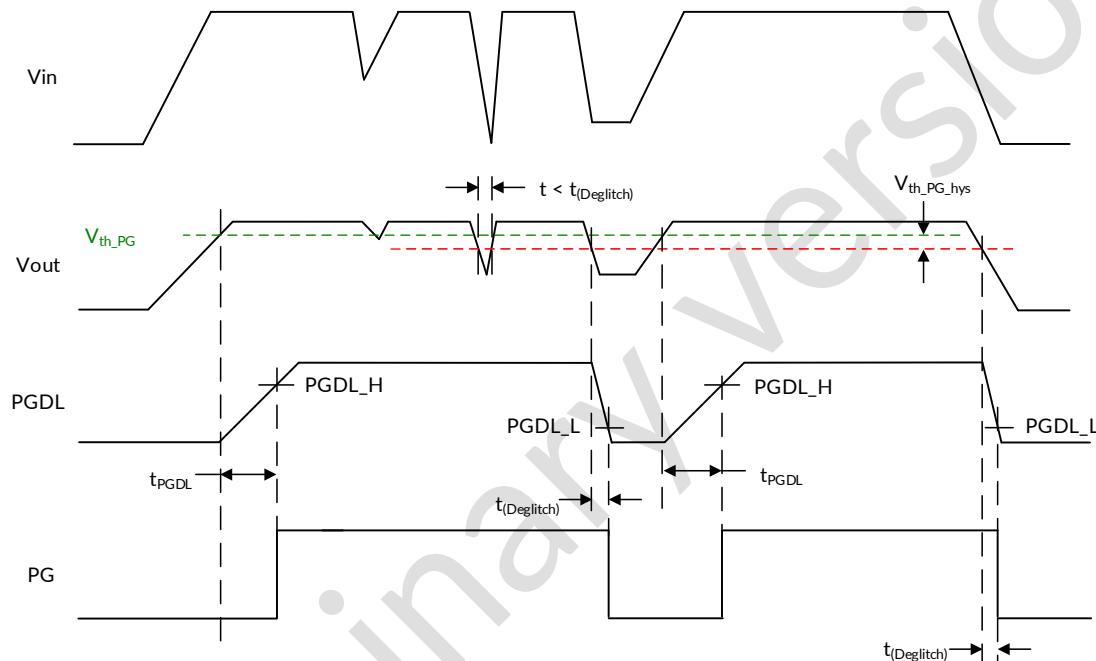

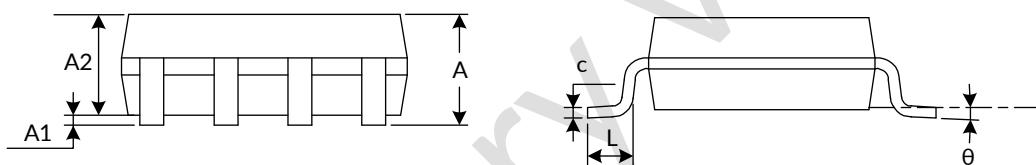

## 13 PACKAGE OUTLINE DIMENSIONS ESOP8<sup>(4)</sup>

**RECOMMENDED LAND PATTERN** (Unit: mm)

| Symbol            | Dimensions In Millimeters  |       | Dimensions In Inches       |       |

|-------------------|----------------------------|-------|----------------------------|-------|

|                   | Min                        | Max   | Min                        | Max   |

| A <sup>(1)</sup>  |                            | 1.650 |                            | 0.065 |

| A1                | 0.050                      | 0.150 | 0.002                      | 0.006 |

| A2                | 1.300                      | 1.500 | 0.051                      | 0.059 |

| b                 | 0.390                      | 0.470 | 0.015                      | 0.019 |

| c                 | 0.200                      | 0.240 | 0.007                      | 0.010 |

| D <sup>(1)</sup>  | 4.800                      | 5.000 | 0.189                      | 0.197 |

| e                 | 1.270 (BSC) <sup>(2)</sup> |       | 0.050 (BSC) <sup>(2)</sup> |       |

| D1                | 3.100 (REF) <sup>(3)</sup> |       | 0.122 (REF) <sup>(3)</sup> |       |

| E2                | 2.210 (REF) <sup>(3)</sup> |       | 0.087 (REF) <sup>(3)</sup> |       |

| E                 | 5.800                      | 6.200 | 0.228                      | 0.244 |

| E1 <sup>(1)</sup> | 3.800                      | 4.000 | 0.150                      | 0.157 |

| L                 | 0.500                      | 0.800 | 0.019                      | 0.032 |

| θ                 | 0°                         | 8°    | 0°                         | 8°    |

NOTE:

1. Plastic or metal protrusions of 0.15mm maximum per side are not included.

2. BSC (Basic Spacing between Centers), "Basic" spacing is nominal.

3. REF is the abbreviation for Reference.

4. This drawing is subject to change without notice.

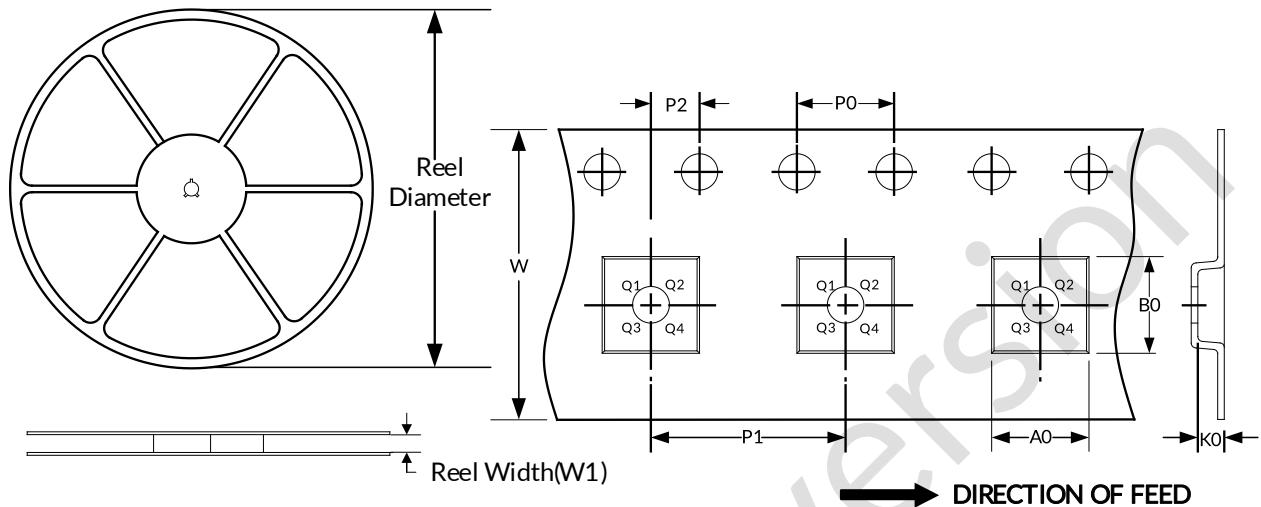

## 14 TAPE AND REEL INFORMATION

### REEL DIMENSIONS

### TAPE DIMENSION

NOTE: The picture is only for reference. Please make the object as the standard.

### KEY PARAMETER LIST OF TAPE AND REEL

| Package Type | Reel Diameter | Reel Width (mm) | A0 (mm) | B0 (mm) | K0 (mm) | P0 (mm) | P1 (mm) | P2 (mm) | W (mm) | Pin1 Quadrant |

|--------------|---------------|-----------------|---------|---------|---------|---------|---------|---------|--------|---------------|

| ESOP8        | 13"           | 12.4            | 6.40    | 5.40    | 2.10    | 4.0     | 8.0     | 2.0     | 12.0   | Q1            |

NOTE:

1. All dimensions are nominal.

2. Plastic or metal protrusions of 0.15mm maximum per side are not included.

## **IMPORTANT NOTICE AND DISCLAIMER**

Jiangsu RUNIC Technology Co., Ltd. will accurately and reliably provide technical and reliability data (including data sheets), design resources (including reference designs), application or other design advice, WEB tools, safety information and other resources, without warranty of any defect, and will not make any express or implied warranty, including but not limited to the warranty of merchantability Implied warranty that it is suitable for a specific purpose or does not infringe the intellectual property rights of any third party.

These resources are intended for skilled developers designing with RUNIC products You will be solely responsible for: (1) Selecting the appropriate products for your application; (2) Designing, validating and testing your application; (3) Ensuring your application meets applicable standards and any other safety, security or other requirements; (4) RUNIC and the RUNIC logo are registered trademarks of RUNIC INCORPORATED. All trademarks are the property of their respective owners; (5) For change details, review the revision history included in any revised document. The resources are subject to change without notice. Our company will not be liable for the use of this product and the infringement of patents or third-party intellectual property rights due to its use.