# **Programmable Current Limit Switches**

### **1 FEATURES**

- Wide Input Voltage Range from 4.5V to 40V with Surge up to 45V

- Extremely Low R<sub>DS(ON)</sub> for the Integrated Protection Switch: 80mΩ

- Programmable Soft-Start Time

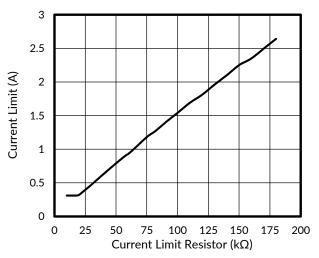

- Programmable Current Limit from 350mA to 2.5A

- ±7% Current Limit Accuracy at T<sub>A</sub> = +25°C

- Enable Interface Pin

- Short-Circuit Protection

- Over-Voltage Protection

- Fault Output for Thermal Shutdown, Short-Circuit, UVLO and OVP

- -40°C to 125°C Operating Temperature Range

## 2 APPLICATIONS

- White Goods, Appliances

- Set-Top Boxes, DVD and Gaming Consoles

- HDD and SSD Drives

- Smart Meters, Gas Analyzers

- Smart Load Switches/USB Switches

- Adapter Power Devices

### **3 DESCRIPTIONS**

The RS2604 is compact, feature rich eFuse with a full suite of protection functions. The wide operating voltage allows control of many popular DC buses. The high precision at room temperature and wide range of current limit provide excellent character and make the RS2604 well suited for many system protection applications.

Load, source and device protection are provided with multiple programmable features including over-current (OC), over-voltage (OV) and under-voltage (UV). 3% threshold accuracy for UV and OV, ensures tight supervision of bus voltages and eliminates the need for supervisor circuitry. Fault flag output (nFLT) is provided for system status monitoring and downstream load control.

The RS2604 is designed to operate over a temperature range of -40°C to 125°C.

#### Device Information (1)

| PART NUMBER                                                           | PACKAGE   | BODY SIZE (NOM) |  |  |  |  |  |  |

|-----------------------------------------------------------------------|-----------|-----------------|--|--|--|--|--|--|

| RS2604                                                                | UDFN2X3-8 | 2.00mm × 3.00mm |  |  |  |  |  |  |

| (1) For all available packages, see the orderable addendum at the end |           |                 |  |  |  |  |  |  |

For all available packages, see the orderable addendum at the end of the data sheet.

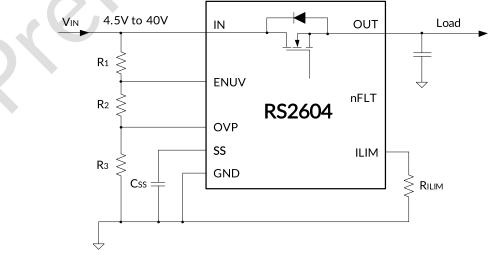

## **4 TYPICAL APPLICATION CIRCUIT**

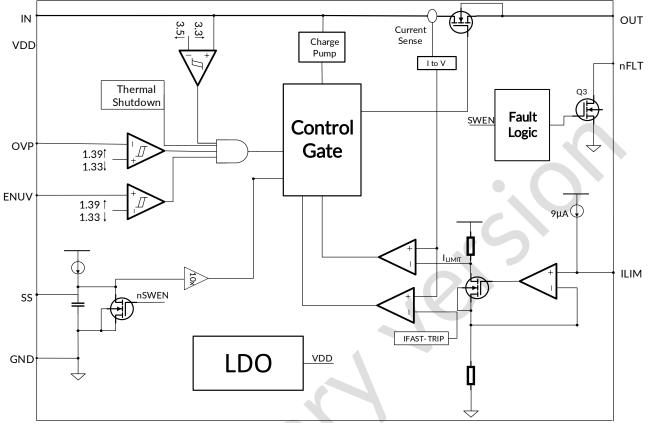

## **5 FUNCTION BLOCK DIAGRAM**

## **Table of Contents**

| 1 FEATURES                                                      | 1  |

|-----------------------------------------------------------------|----|

| 2 APPLICATIONS                                                  | 1  |

| 3 DESCRIPTIONS                                                  | 1  |

| 4 TYPICAL APPLICATION CIRCUIT                                   | 1  |

| 5 FUNCTION BLOCK DIAGRAM                                        | 2  |

| 6 REVISION HISTORY                                              |    |

| 7 PACKAGE/ORDERING INFORMATION <sup>(1)</sup>                   | 5  |

| 8 PIN CONFIGURATIONS                                            | 6  |

| 9 SPECIFICATIONS                                                |    |

| 9.1 Absolute Maximum Ratings                                    |    |

| 9.2 ESD Ratings                                                 | 7  |

| 9.3 Recommended Operating Rating                                |    |

| 9.4 Electrical Characteristics                                  |    |

| 9.5 Timing Requirements                                         | 9  |

| 9.6 Parametric Measurement Information                          |    |

| 9.7 Typical Performance Characteristics                         |    |

| 10 DETAILED DESCRIPTION                                         |    |

| 10.1 Overview                                                   | 15 |

| 10.2 Enable and Adjusting Under-Voltage Lockout (UVLO)          |    |

| 10.3 Over-Voltage Protection (OVP)                              | 15 |

| 10.4 Hot-Plug-In and In-Rush Current Control                    | 15 |

| 10.5 Over-Load and Short-Circuit Protections                    | 16 |

| 10.6 Over-Load Protection                                       | 17 |

| 10.7 Short-Circuit Protection                                   | 17 |

| 10.8 Start-Up with Short on Output                              | 17 |

| 10.9 Constant Current Limit Behavior during Over-Current Faults | 17 |

| 10.10 Fault Response                                            | 18 |

| 10.11 IN, OUT and GND Pins                                      | 18 |

| 10.12 Thermal Shutdown                                          | 18 |

| 10.13 Shutdown Control                                          | 18 |

| 11 PACKAGE OUTLINE DIMENSIONS                                   | 19 |

| 12 TAPE AND REEL INFORMATION                                    | 20 |

## **6 REVISION HISTORY**

Note: Page numbers for previous revisions may different from page numbers in the current version.

| VERSION | Change Date | Change Item                                                                                             |

|---------|-------------|---------------------------------------------------------------------------------------------------------|

| A.0     | 2024/03/13  | Preliminary version completed                                                                           |

| A.0.1   | 2025/03/25  | 1. Add FUNCTION BLOCK DIAGRAM and DETAILED DESCRIPTION<br>2. Update TYPICAL PERFORMANCE CHARACTERISTICS |

## 7 PACKAGE/ORDERING INFORMATION (1)

| PRODUCT | ORDERING<br>NUMBER | TEMPERATURE<br>RANGE | PACKAGE<br>LEAD | PACKAGE<br>MARKING <sup>(2)</sup> | MSL <sup>(3)</sup> | PACKAGE OPTION     |

|---------|--------------------|----------------------|-----------------|-----------------------------------|--------------------|--------------------|

| RS2604  | RS2604YTDB8        | -40°C ~125°C         | UDFN2X3-8       | 2604                              | MSL3               | Tape and Reel,3000 |

NOTE:

(1) This information is the most current data available for the designated devices. This data is subject to change without notice and revision of this document. For browser-based versions of this data sheet, refer to the right-hand navigation.

(2) There may be additional marking, which relates to the lot trace code information (data code and vendor code), the logo or the environmental category on the device.

(3) RUNIC classify the MSL level with using the common preconditioning setting in our assembly factory conforming to the JEDEC industrial standard J-STD-20F, Please align with RUNIC if your end application is quite critical to the preconditioning setting or if you have special requirement.

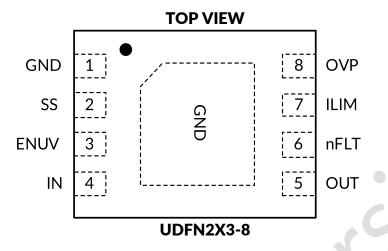

## **8 PIN CONFIGURATIONS**

### **PIN DESCRIPTION**

| PIN | NAME | DESCRIPTION                                                                                                                                                                                                                                          |

|-----|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1   | GND  | Ground                                                                                                                                                                                                                                               |

| 2   | SS   | Soft-Start Pin. A capacitor from this pin to GND sets the ramp rate of output voltage at device turn-on.                                                                                                                                             |

| 3   | ENUV | Enable and Under-Voltage Lockout Input. Input for setting programmable under-voltage lockout threshold. An under-voltage event will open internal FET and assert nFLT to indicate power-failure. When pulled to GND, resets the thermal fault latch. |

| 4   | IN   | Power Input Pin. Power input and supply voltage of the device.                                                                                                                                                                                       |

| 5   | OUT  | Power Output Pin.                                                                                                                                                                                                                                    |

| 6   | nFLT | Fault Event Indicator Pin. Fault event indicator, goes low to indicate fault condition due to under-<br>voltage, over-voltage, short-circuit and thermal shutdown event. A fast-trip does not trigger fault.<br>It is an open drain output.          |

| 7   | ILIM | Current Limit Programming Pin. A resistor from this pin to GND will set the over-load and short-<br>circuit limit. Do not float this pin.                                                                                                            |

| 8   | OVP  | Over-Voltage Protection Pin. Input for setting programmable over-voltage protection threshold.<br>An over-voltage event will open the internal FET and assert nFLT to indicate over-voltage.                                                         |

## 9 SPECIFICATIONS

### 9.1 Absolute Maximum Ratings

over operating free-air temperature range (unless otherwise noted)<sup>(1)</sup>

|                                                |           | MIN  | MAX  | UNIT |

|------------------------------------------------|-----------|------|------|------|

| IN, OUT, ENUV, nFLT, OVP pins Voltage          |           | -0.3 | 45   | V    |

| SS, ILIM Voltage                               |           | -0.3 | 6.0  | V    |

| Package thermal impedance $^{(2)},\theta_{JA}$ | UDFN2X3-8 |      | 62.9 | °C/W |

| Junction temperature <sup>(3)</sup> , TJ       |           | -40  | 150  | °C   |

| Storage temperature, T <sub>stg</sub>          |           | -65  | 150  | °C   |

| Lead Temperature (Soldering,10secs)            |           |      | 260  | °C   |

(1) Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Conditions is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

(2) The package thermal impedance is calculated in accordance with JESD-51.

(3) The maximum power dissipation is a function of  $T_{J(MAX)}$ ,  $R_{\theta JA}$ , and  $T_A$ . The maximum allowable power dissipation at any ambient temperature is  $P_D = (T_{J(MAX)} - T_A) / R_{\theta JA}$ . All numbers apply for packages soldered directly onto a PCB.

### 9.2 ESD Ratings

The following ESD information is provided for handling of ESD-sensitive devices in an ESD protected area only.

|                                            |                            | VALUE | UNIT |

|--------------------------------------------|----------------------------|-------|------|

|                                            | Human-Body Model (HBM)     | ±2000 | V    |

| V <sub>(ESD)</sub> Electrostatic discharge | Charged-Device Model (CDM) | ±1000 | v    |

|                                            | Latch-Up (LU)              | ±200  | mA   |

### ESD SENSITIVITY CAUTION

ESD damage can range from subtle performance degradation to complete device failure. Precision integrated circuits may be more susceptible to damage because very small parametric changes could cause the device not to meet its published specifications.

### 9.3 Recommended Operating Rating

|                                      | MIN | MAX | UNIT |

|--------------------------------------|-----|-----|------|

| Supply Input Voltage                 | 4.5 | 40  | V    |

| Operating Junction Temperature Range | -40 | 125 | °C   |

## **9.4 Electrical Characteristics**

$(V_{IN} = 4.5V \text{ to } 40V, V_{ENUV} = 2V, V_{OVP} = 0V, R_{ILIM} = 160k\Omega, C_{SS} = 1.2nF, nFLT = Open, T_A = 25^{\circ}C, unless otherwise noted.)$ <sup>(1)</sup>

|                                         | SYMBIL             | CONDITIONS                                                        | MIN <sup>(2)</sup> | TYP <sup>(3)</sup> |     |     |

|-----------------------------------------|--------------------|-------------------------------------------------------------------|--------------------|--------------------|-----|-----|

| POWER SUPPLY AND CURRENTS               |                    |                                                                   |                    |                    |     |     |

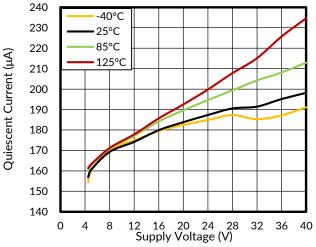

| Power Input Voltage Range               | VIN                |                                                                   | 4.5                |                    | 40  | V   |

| Under-Voltage Lockout Threshold         | VUVLO              | VIN Rising                                                        |                    | 3.5                |     | V   |

| Under-Voltage Lockout Threshold         | Vuvlo hy           |                                                                   |                    | 0.2                |     | V   |

| Hysteresis                              | -                  |                                                                   |                    |                    |     |     |

| Supply Current, Enabled                 | lq                 | $V_{ENUV} = 2V, V_{IN} = 12V$                                     |                    | 175                |     | μA  |

| Supply Current, Disabled                | Isd                | V <sub>ENUV</sub> = 0V, V <sub>IN</sub> = 12V                     |                    | 1.5                | 10  | μA  |

| OVER-VOLTAGE PROTECTION (OVP) IN        |                    | 1                                                                 | •                  |                    |     |     |

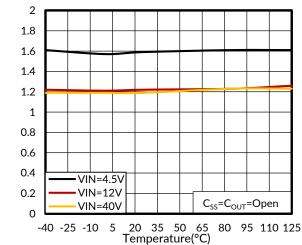

| Over-Voltage Threshold Voltage, Rising  | Vovpr              | OVP Rising                                                        |                    | 1.39               |     | V   |

| Over-Voltage Threshold Voltage, Falling | Vovpf              |                                                                   |                    | 1.33               |     | V   |

| OVP Input Leakage Current               | IOVP               | 0V≤V <sub>OVP</sub> ≤ 40V                                         |                    | 0                  | 0.1 | μA  |

| ENABLE AND UNDER-VOLTAGE LOCKO          | UT (ENUV) II       | NPUT                                                              |                    |                    |     |     |

| ENUV Threshold Voltage, Falling         | $V_{ENF}$          |                                                                   |                    | 1.39               |     | V   |

| ENUV Threshold Voltage, Rising          | $V_{\text{ENR}}$   | ENUV Rising                                                       |                    | 1.33               |     | V   |

| ENUV Input Leakage Current              | Ienuv              | 0V≤V <sub>ENUV</sub> ≤ 40V                                        |                    | 0                  | 0.1 | μA  |

| SOFT-START: OUTPUT RAMP CONTROL         | . (SS)             |                                                                   |                    |                    |     |     |

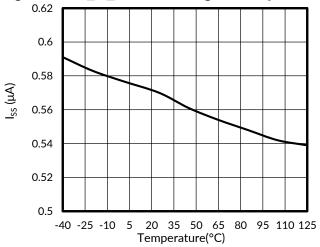

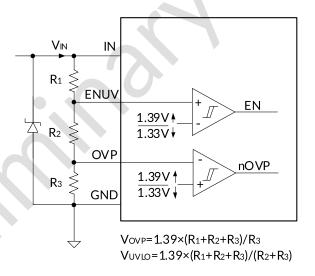

| SS Charging Current                     | lss                | V <sub>SS</sub> =0V                                               |                    | 0.56               |     | μΑ  |

| SS Discharging Resistance               | Rss                | ENUV=0V                                                           |                    | 4.8                |     | kΩ  |

| SS Maximum Capacitor Voltage            | Vssmax             |                                                                   |                    | 5                  |     | V   |

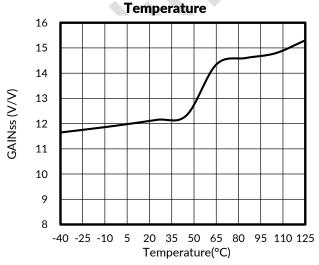

| SS to OUT Gain                          | GAINss             | ΔV <sub>OUT</sub> /ΔV <sub>SS</sub>                               |                    | 11.5               |     | V/V |

| <b>CURRENT LIMIT PROGRAMMING (ILIM)</b> |                    |                                                                   | •                  |                    |     |     |

| ILIM Pin Bias Current                   | ILIM_Bias          | ILIM=0V                                                           |                    | 9                  |     | μA  |

|                                         |                    | RLIMIT=160kΩ, 25°C                                                |                    | 2.5                |     | А   |

| Current Limit                           | Iilim              | RLIMIT=Short, 25°C                                                |                    | 0.3                |     | Α   |

| Fast-Trip Comparator Threshold          | IFAST_TRIP         |                                                                   | 1                  | L.8×Ilimit         |     | Α   |

| ILIM Open Resistor Detect Threshold     | VILIM_OPEN         | VILIM rising, RILIM = Open                                        |                    | 3                  |     | V   |

| MOSFET-POWER SWITCH                     | - F                | •                                                                 |                    |                    |     |     |

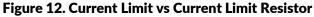

| FET On-Resistance                       | R <sub>Ds</sub>    |                                                                   |                    | 80                 |     | mΩ  |

| PASS FET OUTPUT (OUT)                   |                    | 1                                                                 |                    |                    |     |     |

| OUT Bias Current in off State           | Ilkg_out           | V <sub>ENUV</sub> = 0V,<br>V <sub>OUT</sub> = 0V (Sourcing)       |                    | 0.1                | 0.5 | μA  |

| Discharge Resistor                      | R <sub>DIS</sub>   | V <sub>ENUV</sub> = 0V,<br>V <sub>OUT</sub> = 300mV (Sinking)     |                    | 5                  |     | kΩ  |

| FAULT FLAG (nFLT)                       |                    |                                                                   |                    |                    |     |     |

| nFLT Pull-Down Resietance               | RnFLT              | Device in fault condition,<br>$V_{ENUV} = 0V$ , $I_{nFLT} = 10mA$ |                    | 130                |     | Ω   |

| nFLT Input Leakage Current              | InFLT              | 0V≤V <sub>nFLT</sub> ≤ 40V                                        |                    | 0                  | 0.1 | μA  |

| THERMAL SHUTDOWN                        |                    |                                                                   |                    |                    |     |     |

| Thermal Shutdown Temperature            | T <sub>SD</sub>    | T」 Increasing                                                     |                    | 145                |     | °C  |

| Thermal Shutdown Hysteresis             | T <sub>SD_HY</sub> |                                                                   |                    | 25                 |     | °C  |

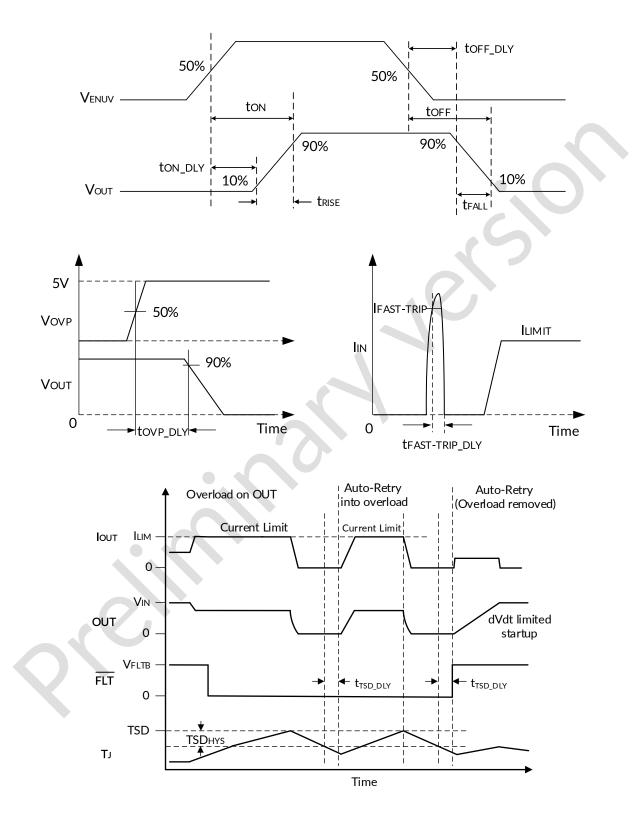

## 9.5 Timing Requirements

$(V_{IN} = 12V, V_{ENUV} = 2V, V_{OVP} = 0V, R_{ILIM} = 160k\Omega, C_{SS} = 1.2nF, nFLT = Open, T_A = 25^{\circ}C, unless otherwise noted.)$ <sup>(1)</sup>

| PARAMETER                                                          | SYMBIL              | CONDITIONS                                                          | <b>MIN</b> <sup>(2)</sup> | <b>TYP</b> <sup>(3)</sup> | MAX <sup>(2)</sup> | UNITS |

|--------------------------------------------------------------------|---------------------|---------------------------------------------------------------------|---------------------------|---------------------------|--------------------|-------|

| ENABLE AND UNDER-VOLTAGE LC                                        | OCKOUT (ENU         | JV) INPUT                                                           |                           |                           |                    |       |

| Turn-Off delay                                                     | Toff_dly            | ENUV50%↓ to Vou⊤90%↓,<br>with Css=Cou⊤=Open                         |                           | 1.2                       |                    | μs    |

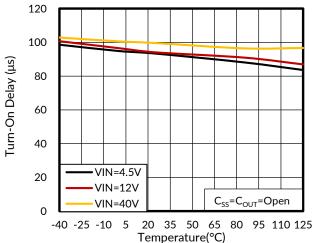

| Turn-On delay                                                      | T <sub>ON_DLY</sub> | ENUV50%↑ to Vou⊤10%↑,<br>with Css=Cou⊤=Open                         |                           | 96                        |                    | μs    |

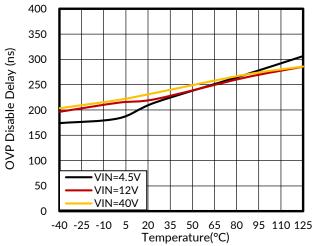

| OVER-VOLTAGE PROTECTION (OV                                        | P) INPUT            |                                                                     |                           |                           |                    |       |

| OVP disable delay                                                  | TOVP_DLY            | ОVР50%↑ to Vо∪т90%↓                                                 |                           | 0.2                       |                    | μs    |

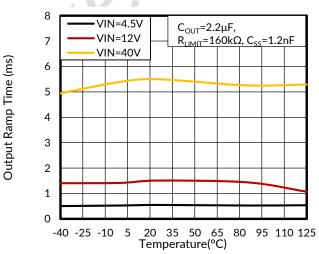

| SOFT-START: OUTPUT RAMP CON                                        | TROL (SS)           |                                                                     |                           |                           |                    |       |

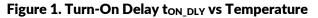

|                                                                    |                     | ENUV50%↑ to V <sub>OUT</sub> 90%↑,<br>with Css = Open, Coυτ = 2.2μF |                           | 125                       |                    | μs    |

| Output Ramp Time                                                   | trise               | ENUV50%↑ to Vouт90%↑,<br>with Css =1.2nF, Cout =2.2μF               | 6                         | 1.5                       |                    | ms    |

| CURRENT LIMIT PROGRAMMING (                                        | ILIM)               |                                                                     |                           |                           |                    |       |

| Fast-Trip Comparator Delay                                         | tfast-trip_dly      |                                                                     |                           | 1                         |                    | μs    |

| THERMAL SHUTDOWN (TSD)                                             |                     |                                                                     |                           |                           | •                  |       |

| Retry Delay after Thermal Shutdown<br>Recovery, TJ < [TTSD - 25°C] |                     |                                                                     |                           | 130                       |                    | ms    |

(1) Electrical table values apply only for factory testing conditions at the temperature indicated. Factory testing conditions result in very limited self-heating of the device.

(2) Limits are 100% production tested at 25°C. Limits over the operating temperature range are ensured through correlations using statistical quality control (SQC) method.

(3) Typical values represent the most likely parametric norm as determined at the time of characterization. Actual typical values may vary over time and will also depend on the application and configuration.

www.run-ic.com

## 9.6 Parametric Measurement Information

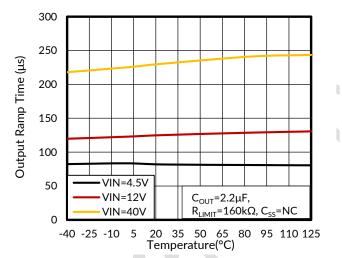

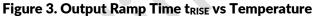

## 9.7 Typical Performance Characteristics

NOTE: The graphs and tables provided following this note are a statistical summary based on a limited number of samples and are provided for informational purposes only.

Furn-Off Delay (µs)

Figure 5. OVP Disable Delay t<sub>OVP\_DLY</sub> vs Temperature

Figure 2. Turn-Off Delay toFF\_DLY vs Temperature

Figure 4. Output Ramp Time t<sub>RISE</sub> vs Temperature

Figure 6. Quiescent Current vs Supply Voltage

## **Typical Performance Characteristics**

NOTE: The graphs and tables provided following this note are a statistical summary based on a limited number of samples and are provided for informational purposes only.

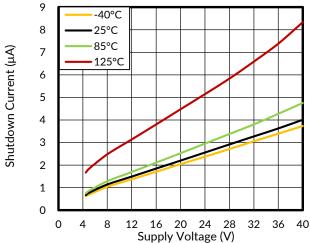

Figure 7. Shutdown Current vs Supply Voltage

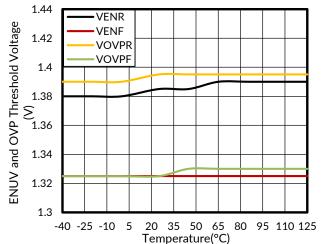

Figure 9. ENUV and OVP Threshold Voltage vs

Figure 11. GAINss vs Temperature

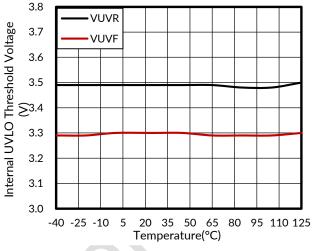

Figure 8. UVLO Threshold Voltage vs Temperature

Figure 10. Iss vs Temperature

## **Typical Performance Characteristics**

NOTE: The graphs and tables provided following this note are a statistical summary based on a limited number of samples and are provided for informational purposes only.

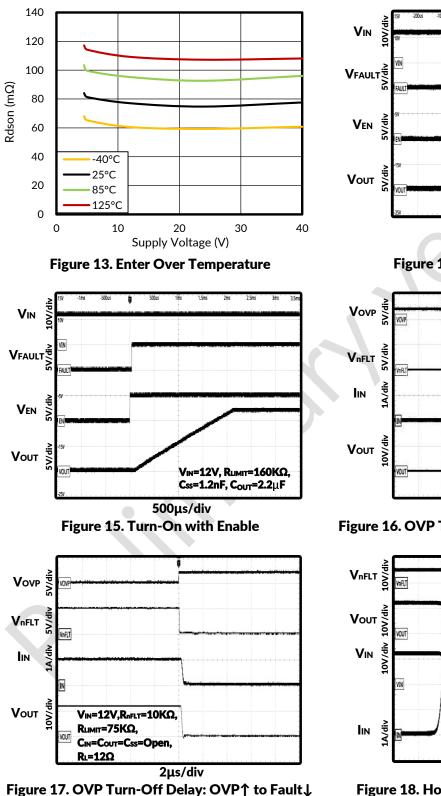

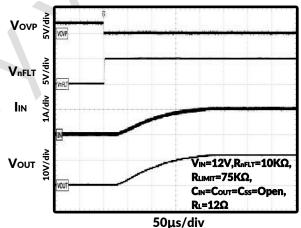

Figure 14. Turn-On with Enable

100µs/div

VIN=12V, RLIMIT=160KΩ,

Css=Open, Cout=2.2µF

Figure 16. OVP Turn-On Delay: OVP↓ to Output Ramp↑

## **Typical Performance Characteristics**

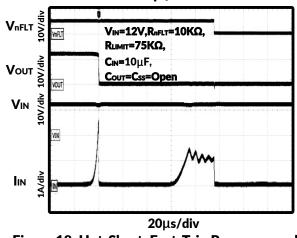

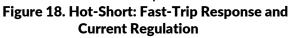

NOTE: The graphs and tables provided following this note are a statistical summary based on a limited number of samples and are provided for informational purposes only.

Figure 19. Hot-Short: Fast-Trip Response (Zoomed)

## **10 DETAILED DESCRIPTION**

### 10.1 Overview

The RS2604 is compact, feature rich eFuse with a full suite of protection functions. The wide operating voltage allows control of many popular DC buses. The high precision at room temperature and wide range of current limit provide excellent character and make the RS2604 well suited for many system protection applications. Load, source and device protection are provided with multiple programmable features including over-current (OC), over-voltage (OV) and under-voltage (UV). 3% threshold accuracy for UV and OV, ensures tight supervision of bus voltages and eliminates the need for supervisor circuitry. Fault flag output (nFLT) is provided for system status monitoring and downstream load control.

The RS2604 is designed to operate over a temperature range of -40°C to 125°C.

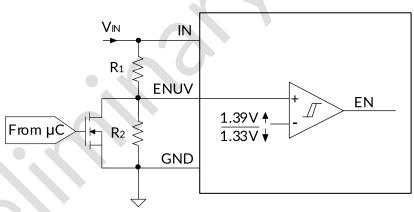

### 10.2 Enable and Adjusting Under-Voltage Lockout (UVLO)

The ENUV pin controls the on/off state of the internal FET. A voltage  $V_{ENUV} < V_{ENF}$  on this pin turns off the internal FET, thus disconnecting IN from OUT.

The internal de-glitch delay on ENUV falling edge is kept low for quick detection of power failure. For applications where a higher de-glitch delay on ENUV is desired, or when the supply is particularly noisy, it is recommended to use an external filter capacitor from the ENUV terminal to GND.

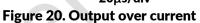

The under-voltage lockout threshold can be programmed by using an external resistor divider from the supply IN terminal to the ENUV terminal to GND as shown in Figure 21. When an under-voltage or input power fail event is detected, the internal FET is quickly turned off, and nFLT is asserted. If the under-voltage lockout function is not needed, the ENUV pin should be connected to the IN terminal. The ENUV terminal should not be left floating. RS2604 also implement internal under voltage lockout (UVLO) circuitry on the IN pin. The devices get disabled when the IN terminal voltage falls below internal UVLO threshold V<sub>UVF</sub>.

Figure 21. UVLO and OVP Thresholds Set by  $R_1$ ,  $R_2$  and  $R_3$

### **10.3 Over-Voltage Protection (OVP)**

RS2604 incorporate circuits to protect the system during over-voltage conditions. A resistor divider, connected from the supply to OVP terminal to GND (as shown in Figure 21), programs the over-voltage threshold. A voltage more than V<sub>OVPR</sub> on the OVP pin turns off the internal FET and protects the downstream load. This pin should be tied to GND when not used.

### 10.4 Hot-Plug-In and In-Rush Current Control

RS2604 are designed to control the in-rush current upon insertion of a card into a live backplane or other "hot" power source. This limits the voltage sag on the backplane's supply voltage and prevents unintended resets of the system power. A slew rate controlled start-up (SS) also helps to eliminate conductive and radiated

(1)

interference. An external capacitor from the SS pin to GND defines the slew rate of the output voltage at poweron (as shown in Figure 22). The equation governing slew rate at start-up is shown in Equation 1:

$I_{SS} = \frac{C_{SS}}{GAIN_{SS}} \times \frac{dV_{OUT}}{dt}$ where:  $I_{SS} = 0.56\mu A (TYP)$

$dV_{OUT}/dt = Desired output slew rate$  $GAINss = <math>\Delta V_{OUT}/\Delta V_{SS}$  gain = 11.5

### Figure 22. Output Ramp Time $t_{dVdT}$ is Set by $C_{dVdT}$

The total ramp time (t<sub>SS</sub>) of V<sub>OUT</sub> from 0 to V<sub>IN</sub> can be calculated using Equation 2:  $t_{SS} = 15.53 \times 10^4 \times V_{IN} \times C_{SS}$ where C<sub>SS</sub> is in Farad.

The in-rush current, I<sub>IN-RUSH</sub> can be calculated as

tss

The SS pin can be left floating to obtain a predetermined slew rate ( $t_{SS}$ ) on the output. When terminal is left floating, the device sets an internal ramp rate of ~50V/ms for output ( $V_{OUT}$ ) ramp.

For systems where load is present during start-up, the current never exceeds the over-current limit set by  $R_{ILIM}$  resistor for the application.

### **10.5 Over-Load and Short-Circuit Protections**

At all times load current is monitored by sensing voltage across an internal sense resistor. During over-load events, current is limited to the current limit ( $I_{\text{LIMIT}}$ ) programmed by  $R_{\text{ILIM}}$  resistor:  $I_{\text{LIMIT}}$  (A)= 15 × 10<sup>-3</sup> ×  $R_{\text{ILIM}}$  (k $\Omega$ )- 0.03 (4)

$I_{\text{LIMIT}}$  (A)= 15 × 10<sup>-3</sup> × R<sub>ILIM</sub> (kΩ)- 0.03  $I_{\text{LIMIT}}$  (A) + 0.03

(5)

$R_{ILIM}(k\Omega) =$

15×10<sup>-3</sup>

where:

ILIMIT is over-load current limit in Ampere.

$R_{\text{ILIM}}$  is the current limit programming resistor in  $k\Omega.$

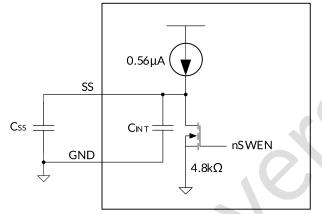

RS2604 incorporate two distinct over-current protection levels: the current limit (I<sub>LIMIT</sub>) and the fast-trip threshold (I<sub>FAST-TRIP</sub>). The fast-trip and current limit operations are shown in Figure 23.

Bias current on ILIM pin directly controls current-limiting behavior of the device, and PCB routing of this node must be kept away from any noisy (switching) signals.

(2)

(3)

### **10.6 Over-Load Protection**

Under overload conditions, the internal current - limiting amplifier adjusts the output current to the current limit value ILIMIT. During the current - limiting regulation, the output voltage will drop, which leads to an increase in the power dissipation of the device. If the device junction temperature reaches the thermal shutdown threshold (T<sub>TSD</sub>), or the output voltage is approximately 1.4V lower than the supply voltage, the internal FET will be turned off. Once in the shutdown state, after the junction temperature  $T_J < [T_{TSD} - 20^{\circ}C]$ , the RS2604 will start an automatic recovery cycle with a duration of  $t_{TSD_DLY}$ . During the shutdown period, the fault pin nFLT will be pulled low to indicate a fault condition.

During the startup of the output voltage, the output capacitor needs to be charged. If the sum of the current used to charge the capacitor and the load current exceeds the set over - current value, over - current protection may be triggered, preventing the chip from starting up. The current for charging the output capacitor is determined by the following formula:

6.44×Cout×e<sup>-6</sup>  $I_{cap} =$

Assuming the output capacitor is  $1\mu$ F and C<sub>ss</sub> is 1nF, the current for charging the output capacitor is 6.44mA, which can be ignored. However, when the C<sub>SS</sub> capacitor is 1pF, the charging current for the capacitor will increase to 644mA. If the set current limit value is 1A at this time, as long as the load current is greater than 0.356A, over current protection may be triggered.

### **10.7 Short-Circuit Protection**

During a transient short-circuit event, the current through the device increases very rapidly. As current limit amplifier cannot respond quickly to this event due to its limited bandwidth, the device incorporates a fast-trip comparator, with a threshold IFAST-TRIP. When the current through the internal FET exceeds IFAST-TRIP (IOUT > IFAST-TRIP), this comparator shuts down the pass device within  $1\mu$ s and terminates the rapid short-circuit peak current. The IFAST-TRIP threshold is dependent on programmed over-load current limit and function of RILIM. See Equation 7 for the calculation.

$I_{FAST-TRIP} = 1.8 \times I_{LIMIT}$

where:

IFAST-TRIP is fast-trip current limit in Ampere.

The fast-trip circuit holds the internal FET off for only a few microseconds, after which the device attempts to turn back on normally, allowing the current limit loop to regulate the output current to ILIMIT. Then, device behaves similarly to over-load condition.

### **10.8 Start-Up with Short on Output**

During start-up into a short-circuit current is limited to ILIMIT. This feature helps in guick fault isolation and hence ensures stability of the DC bus.

### **10.9 Constant Current Limit Behavior during Over-Current Faults**

When  $T_J > 120^{\circ}$ C, there is about 1% to 20% thermal foldback in the current limit value so that the regulated current drops from ILIMIT to ILIMIT'. Eventually, the device shuts down due to over temperature.

Figure 23. Over-Current Protection Levels

17 / 21

(6)

(7)

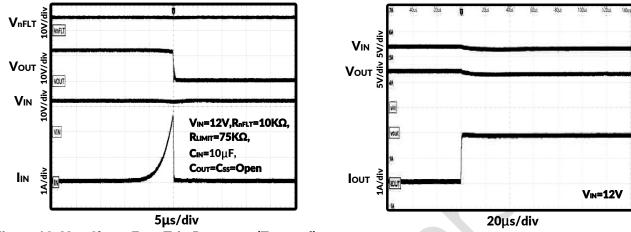

### 10.10 Fault Response

The nFLT pin open drain output is asserted (active low) during under-voltage, over-voltage and thermal shutdown conditions. The nFLT signal remains asserted until the fault condition is removed and the device resumes normal operation. During thermal shutdown, each of the RS2604 commences an auto-recovery cycle  $t_{TSD_DLY}$  after T<sub>J</sub> < [T<sub>TSD</sub> - 20°C].

Connect nFLT pin with a pull-up resistor to input or output voltage rail. The nFLT pin may be left open or tied to GND when not used.

### 10.11 IN, OUT and GND Pins

The IN pin should be connected to the power source. A ceramic bypass capacitor close to the device from IN to GND is recommended to alleviate bus transients. The recommended operating voltage range is 4.5V to 40V. The OUT pin should be connected to the load.  $V_{OUT}$  in the ON condition, is calculated using the Equation 8:  $V_{OUT} = V_{IN} - (R_{DS(ON)} \times I_{OUT})$  (8)

where R<sub>DS(ON)</sub> is the on-resistance of the internal FET. GND terminal is the most negative voltage in the circuit and is used as a reference for all voltage reference unless otherwise specified.

#### **10.12 Thermal Shutdown**

Internal over-temperature shutdown disables/turns off the FET when  $T_J > 150^{\circ}C$  (TYP). Each of the RS2604 commences an auto-recovery cycle  $t_{TSD_DLY}$  after  $T_J$  drops below [ $T_{TSD} - 20^{\circ}C$ ]. During the thermal shutdown, the fault pin nFLT is pulled low to signal a fault condition.

### **10.13 Shutdown Control**

The internal FET and hence the load current can be remotely switched off by taking the ENUV pin below its 1.33V threshold with an open collector or open drain device as shown in Figure 24. Upon releasing the ENUV pin the device turns on with soft-start cycle.

Figure 24. Shutdown Control

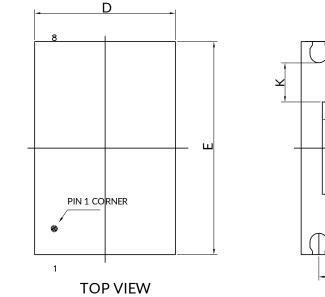

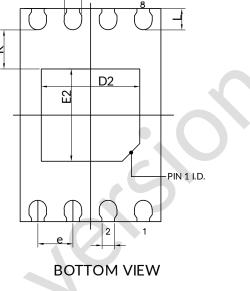

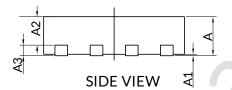

### 11 PACKAGE OUTLINE DIMENSIONS UDFN2X3-8<sup>(4)</sup>

b

| Combal           | Dimensions I                                      | n Millimeters      | Dimension                             | s In Inches        |  |  |

|------------------|---------------------------------------------------|--------------------|---------------------------------------|--------------------|--|--|

| Symbol           | Min                                               | Max                | 0.600 0.020   0.050 0.000   0.01 0.01 | Мах                |  |  |

| A (1)            | 0.500                                             | 0.600              | 0.020                                 | 0.024              |  |  |

| A1               | 0.000                                             | 0.050              | 0.000                                 | 0.002              |  |  |

| A2               | 0.4                                               | 00                 | 0.016                                 |                    |  |  |

| A3               | 0.152 REF <sup>(3)</sup> 0.006 REF <sup>(3)</sup> |                    |                                       |                    |  |  |

| D <sup>(1)</sup> | 1.900                                             | 2.100              | 0.075                                 | 0.083              |  |  |

| E <sup>(1)</sup> | 2.900                                             | 3.100              | 0.114                                 | 0.122              |  |  |

| D2               | 1.400                                             | 1.600              | 0.055                                 | 0.063              |  |  |

| E2               | 1.300                                             | 1.500              | 0.051                                 | 0.059              |  |  |

| e                | 0.500                                             | BSC <sup>(2)</sup> | 0.020                                 | BSC <sup>(2)</sup> |  |  |

| b                | 0.200                                             | 0.300              | 0.008                                 | 0.012              |  |  |

| L                | 0.250                                             | 0.350              | 0.010                                 | 0.014              |  |  |

| К                | 0.500                                             | REF <sup>(3)</sup> | 0.020                                 | REF <sup>(3)</sup> |  |  |

NOTE:

1. Plastic or metal protrusions of 0.075mm maximum per side are not included.

2. BSC (Basic Spacing between Centers), "Basic" spacing is nominal.

3. REF is the abbreviation for Reference.

4. This drawing is subject to change without notice.

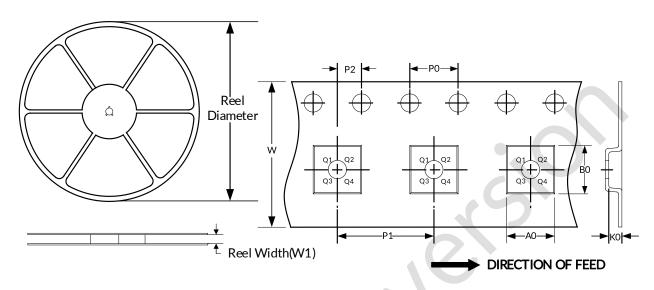

## **12 TAPE AND REEL INFORMATION**

### **REEL DIMENSIONS**

### TAPE DIMENSION

NOTE: The picture is only for reference. Please make the object as the standard.

### **KEY PARAMETER LIST OF TAPE AND REEL**

| Package Type | Reel     | Reel Width | A0   | B0   | K0   | P0   | P1   | P2   | W    | Pin1     |

|--------------|----------|------------|------|------|------|------|------|------|------|----------|

|              | Diameter | (mm)       | (mm) | (mm) | (mm) | (mm) | (mm) | (mm) | (mm) | Quadrant |

| UDFN2X3-8    | 7"       | 9.5        | 2.30 | 3.30 | 0.95 | 4.0  | 4.0  | 2.0  | 8.0  | Q2       |

NOTE:

1. All dimensions are nominal.

2. Plastic or metal protrusions of 0.15mm maximum per side are not included.

## **IMPORTANT NOTICE AND DISCLAIMER**

Jiangsu RUNIC Technology Co., Ltd. will accurately and reliably provide technical and reliability data (including data sheets), design resources (including reference designs), application or other design advice, WEB tools, safety information and other resources, without warranty of any defect, and will not make any express or implied warranty, including but not limited to the warranty of merchantability Implied warranty that it is suitable for a specific purpose or does not infringe the intellectual property rights of any third party.

These resources are intended for skilled developers designing with RUNIC products You will be solely responsible for: (1) Selecting the appropriate products for your application; (2) Designing, validating and testing your application; (3) Ensuring your application meets applicable standards and any other safety, security or other requirements; (4) RUNIC and the RUNIC logo are registered trademarks of RUNIC INCORPORATED. All trademarks are the property of their respective owners; (5) For change details, review the revision history included in any revised document. The resources are subject to change without notice. Our company will not be liable for the use of this product and the infringement of patents or third-party intellectual property rights due to its use.