# 7MHz, Precision, Rail-to-Rail I/O CMOS Operational Amplifier

#### 1 FEATURES

• Gain Bandwidth: 7MHz

Rail-to-Rail Input and Output 3mV Max Vos

Input Voltage Range: -0.1V to +5.6V with Vs = 5.5V

Supply Range: +2.4V to +5.5V

Specified Up to +125°C

Micro Size Packages: SOT23-5

#### 2 APPLICATIONS

Sensors

• Photodiode Amplification

Active Filters

• Test Equipment

• Driving A/D Converters

#### **3 DESCRIPTIONS**

The RS621K offer low voltage operation and rail-to-rail input and output, as well as excellent speed/power consumption ratio, providing an excellent bandwidth (7MHz) and slew rate of  $3.7V/\mu s$ . The opamps are unity gain stable and feature an ultra-low input bias current.

The RS621K has lower offset, which is guaranteed not upper than 3mV at 25°C with Vs = 5V,  $V_{CM} = V_S/2$ .

The devices are ideal for sensor interfaces, active filters and portable applications. The RS621K is specified at the full temperature range of -40°C to +125°C under single or dual power supplies of 2.4V to 5.5V.

#### **Device Information (1)**

| PART NUMBER | PACKAGE | BODY SIZE(NOM) |  |  |  |

|-------------|---------|----------------|--|--|--|

| RS621K      | SOT23-5 | 2.90mm×1.60mm  |  |  |  |

<sup>(1)</sup> For all available packages, see the orderable addendum at the end of the data sheet.

## **Table of Contents**

| 1 FEATURES                           | 1  |

|--------------------------------------|----|

| 2 APPLICATIONS                       | 1  |

| 3 DESCRIPTIONS                       | 1  |

| 4 REVISION HISTORY                   | 3  |

| 5 PACKAGE/ORDERING INFORMATION (1)   | 4  |

| 6 PIN CONFIGURATION AND FUNCTIONS    | 5  |

| 7 SPECIFICATIONS                     | 6  |

| 7.1 Absolute Maximum Ratings         | 6  |

| 7.2 ESD Ratings                      | 6  |

| 7.3 Recommended Operating Conditions | 6  |

| 7.4 Electrical Characteristics       | 7  |

| 7.5 Typical Characteristics          | 9  |

| 8 DETAILED DESCRIPTION               | 13 |

| 8.1 Overview                         | 13 |

| 8.2 Phase Reversal Protection        | 13 |

| 8.3 EMI Rejection Ratio (EMIRR)      | 13 |

| 8.4 EMIRR IN+ Test Configuration     | 14 |

| 9 APPLICATION AND IMPLEMENTATION     | 15 |

| 9.1 Application Note                 | 15 |

| 9.2 25-kHz Low-pass Filter           | 15 |

| 9.3 Design Requirements              | 15 |

| 9.4 Detailed Design Procedure        | 15 |

| 9.5 Application Curve                | 16 |

| 10 LAYOUT                            | 17 |

| 10.1 Layout Guideline                | 17 |

| 10.2 Layout Example                  | 17 |

| 11 PACKAGE OUTLINE DIMENSIONS        | 18 |

| 12 TADE AND DEEL INCODMATION         | 10 |

## **4 REVISION HISTORY**

Note: Page numbers for previous revisions may different from page numbers in the current version.

| VERSION | Change Date                                                                                  | Change Item                                                                                                                                                                                                         |  |  |  |

|---------|----------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| C.1     | C.1 2022/05/19 1. Increase the minimum junction temperature 2. Add TAPE AND REEL INFORMATION |                                                                                                                                                                                                                     |  |  |  |

| C.1.1   | 2024/03/01                                                                                   | Modify packaging naming                                                                                                                                                                                             |  |  |  |

| C.2     | 2025/01/08                                                                                   | <ol> <li>Delete RS621KXC5/RS621BKXC5/RS621KXK/RS621KXM Orderable Device</li> <li>Add MSL on Page 5 in RevC.1.1</li> <li>Add Package thermal impedance on Page 4 in RevC.1.1</li> <li>Update PACKAGE note</li> </ol> |  |  |  |

## 5 PACKAGE/ORDERING INFORMATION (1)

| Orderable<br>Device | Package Type | Pin | Channel | Op Temp(°C)  | Device<br>Marking <sup>(2)</sup> | MSL (3) | Package Qty        |

|---------------------|--------------|-----|---------|--------------|----------------------------------|---------|--------------------|

| RS621KXF            | SOT23-5      | 5   | 1       | -40°C ~125°C | 621K                             | MSL3    | Tape and Reel,3000 |

| RS621BKXF           | SOT23-5      | 5   | 1       | -40°C ~125°C | 621BK                            | MSL3    | Tape and Reel,3000 |

- (1) This information is the most current data available for the designated devices. This data is subject to change without notice and revision of this document. For browser-based versions of this data sheet, refer to the right-hand navigation.

- (2) There may be additional marking, which relates to the lot trace code information (data code and vendor code), the logo or the environmental category on the device.

- (3) RUNIC classify the MSL level with using the common preconditioning setting in our assembly factory conforming to the JEDEC industrial standard J-STD-20F. Please align with RUNIC if your end application is quite critical to the preconditioning setting or if you have special requirement.

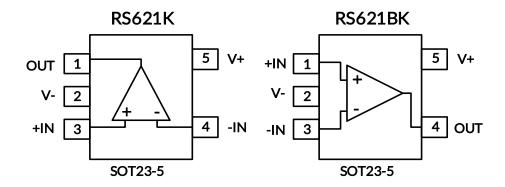

## **6 PIN CONFIGURATION AND FUNCTIONS**

## **PIN DESCRIPTION**

|      | Р       | IN      |         |                                 |  |  |

|------|---------|---------|---------|---------------------------------|--|--|

| NAME | RS621K  | RS621BK | I/O (1) | DESCRIPTION                     |  |  |

|      | SOT23-5 | SOT23-5 |         |                                 |  |  |

| -IN  | 4       | 3       | I       | Negative (inverting) input      |  |  |

| +IN  | 3       | 1       | I       | Positive (noninverting) input   |  |  |

| OUT  | 1       | 4       | 0       | Output                          |  |  |

| V-   | 2       | 2       | -       | Negative (lowest) power supply  |  |  |

| V+   | 5       | 5       | -       | Positive (highest) power supply |  |  |

<sup>(1)</sup> I = Input, O = Output.

#### **7 SPECIFICATIONS**

#### 7.1 Absolute Maximum Ratings

Over operating free-air temperature range (unless otherwise noted) (1)

|             |                                         | ·        | MIN        | MAX       | UNIT |

|-------------|-----------------------------------------|----------|------------|-----------|------|

|             | Supply, Vs=(V+) - (V-)                  |          | 7          |           |      |

| Voltage     | Signal input pin <sup>(2)</sup>         |          | (V-)-0.5   | (V+) +0.5 | V    |

|             | Signal output pin (3)                   | (V-)-0.5 | (V+) +0.5  |           |      |

|             | Signal input pin <sup>(2)</sup>         | -10      | 10         | mA        |      |

| Current     | Signal output pin (3)                   | -140     | 140        | mA        |      |

|             | Output short-circuit (4)                | Conti    | Continuous |           |      |

| θμΑ         | Package thermal impedance (5)           | SOT23-5  |            | 230       | °C/W |

|             | Operating range, T <sub>A</sub>         | -40      | 125        |           |      |

| Temperature | Junction, T <sub>J</sub> <sup>(6)</sup> | -40      | 150        | °C        |      |

|             | Storage, T <sub>stg</sub>               | -65      | 150        |           |      |

<sup>(1)</sup> Stresses above these ratings may cause permanent damage. Exposure to absolute maximum conditions for extended periods may degrade device reliability. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those specified is not implied.

- (4) Short-circuit to ground, one amplifier per package.

- (5) The package thermal impedance is calculated in accordance with JESD-51.

- (6) The maximum power dissipation is a function of  $T_{J(MAX)}$ ,  $R_{\theta JA}$ , and  $T_A$ . The maximum allowable power dissipation at any ambient temperature is  $P_D = (T_{J(MAX)} T_A) / R_{\theta JA}$ . All numbers apply for packages soldered directly onto a PCB.

#### 7.2 ESD Ratings

The following ESD information is provided for handling of ESD-sensitive devices in an ESD protected area only.

|                    |                         |                        | VALUE | UNIT |  |

|--------------------|-------------------------|------------------------|-------|------|--|

| V <sub>(ESD)</sub> | Electrostatic discharge | Human-Body Model (HBM) | ±3000 | \ /  |  |

|                    |                         | Machine Model (MM)     | ±200  | V    |  |

#### **ESD SENSITIVITY CAUTION**

ESD damage can range from subtle performance degradation to complete device failure. Precision integrated circuits may be more susceptible to damage because very small parametric changes could cause the device not to meet its published specifications.

## 7.3 Recommended Operating Conditions

Over operating free-air temperature range (unless otherwise noted)

|                                 |               | MIN  | NOM | MAX   | UNIT |

|---------------------------------|---------------|------|-----|-------|------|

| Supply valtage Va- (VI) (V)     | Single-supply | 2.4  |     | 5.5   | \/   |

| Supply voltage, Vs= (V+) - (V-) | Dual-supply   | ±1.2 |     | ±2.75 | V    |

<sup>(2)</sup> Input terminals are diode-clamped to the power-supply rails. Input signals that can swing more than 0.5V beyond the supply rails should be current-limited to 10mA or less.

<sup>(3)</sup> Output terminals are diode-clamped to the power-supply rails. Output signals that can swing more than 0.5V beyond the supply rails should be current-limited to  $\pm 140$ mA or less.

## 7.4 Electrical Characteristics

(At  $T_A$  = +25°C,  $V_S$ =5V,  $R_L$  = 10k $\Omega$  connected to  $V_S$ /2, and  $V_{OUT}$  =  $V_S$ /2, Full  $^{(9)}$  = -40°C to 125°C, unless otherwise noted.)  $^{(1)}$

|                                                                            | DADAMETED                       | COMPITIONS                           |      |                    | RS621K |                    |        |  |  |

|----------------------------------------------------------------------------|---------------------------------|--------------------------------------|------|--------------------|--------|--------------------|--------|--|--|

|                                                                            | PARAMETER                       | CONDITIONS                           | T,   | MIN <sup>(2)</sup> | TYP(3) | MAX <sup>(2)</sup> | UNITS  |  |  |

| POWER SUPPLY       Vs     Operating Voltage Range     25°C     2.4     5.5 |                                 |                                      |      |                    |        |                    |        |  |  |

| Vs                                                                         | Operating Voltage Range         |                                      | 25°C | 2.4                |        | 5.5                | V      |  |  |

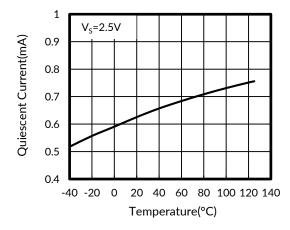

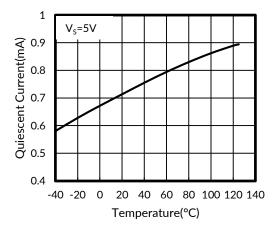

| Ιq                                                                         | Quiescent Current Per Amplifier |                                      | 25°C |                    | 700    | 900                | μΑ     |  |  |

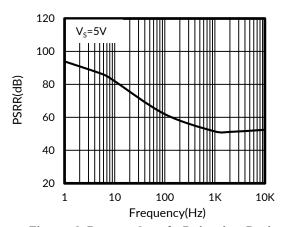

| DCDD                                                                       | Power-Supply Rejection Ratio    | Vs=2.4V to 5.5V,                     | 25°C | 75                 | 92     |                    | 40     |  |  |

| PSRR                                                                       | Power-Supply Rejection Ratio    | V <sub>CM</sub> =(V-)+0.5V           | Full | 65                 |        |                    | dB     |  |  |

| INPUT                                                                      |                                 |                                      |      |                    |        |                    |        |  |  |

| Vos                                                                        | Input Offset Voltage            | V <sub>CM</sub> =0V to 3.5V          | 25°C | -3                 | 0.8    | 3                  | mV     |  |  |

| V <sub>os</sub> T <sub>c</sub>                                             | Input offset voltage drift      |                                      | Full |                    | 2      |                    | μV/°C  |  |  |

| IB                                                                         | Input Bias Current (4) (5)      |                                      | 25°C |                    | 1      | 10                 | pА     |  |  |

| los                                                                        | Input Offset Current (4)        |                                      | 25°C |                    | 1      | 10                 | pА     |  |  |

| $V_{CM}$                                                                   | Common-Mode Voltage Range       | Vs= 5.5V                             | 25°C | -0.1               |        | 5.6                | >      |  |  |

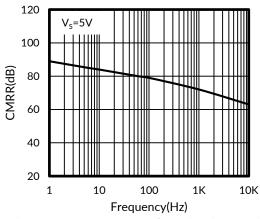

|                                                                            | Common-Mode Rejection Ratio     | Vs= 5.5V,                            | 25°C | 75                 | 95     |                    | dB     |  |  |

| CMRR                                                                       |                                 | V <sub>CM</sub> =-0.1V to 4V         | Full | 68                 |        |                    |        |  |  |

| CIVIKK                                                                     | Common-wode Rejection Ratio     | Vs= 5.5V,                            | 25°C | 63                 | 80     |                    |        |  |  |

|                                                                            |                                 | V <sub>CM</sub> =-0.1V to 5.6V       | Full | 57                 |        |                    |        |  |  |

| OUTPU                                                                      | Т                               |                                      |      |                    |        |                    |        |  |  |

|                                                                            |                                 | R <sub>L</sub> =10KΩ,                | 25°C | 95                 | 110    |                    | dB     |  |  |

| ۸                                                                          | Open-Loop Voltage Gain          | Vo=0.15V to 4.85V                    | Full | 85                 |        |                    |        |  |  |

| Aol                                                                        | Open-Loop Voltage Gain          | $R_L=2K\Omega$ ,                     | 25°C | 100                | 120    |                    |        |  |  |

|                                                                            |                                 | Vo= 0.05V to 4.95V                   | Full | 92                 |        |                    |        |  |  |

|                                                                            | Output Suina Franc Bail         | R <sub>L</sub> =2KΩ                  | 25°C |                    | 40     |                    | \/     |  |  |

|                                                                            | Output Swing From Rail          | R <sub>L</sub> =10KΩ                 | 25°C |                    | 7      |                    | mV     |  |  |

| lout                                                                       | Output Current Source (6) (7)   |                                      | 25°C |                    | 120    |                    | mA     |  |  |

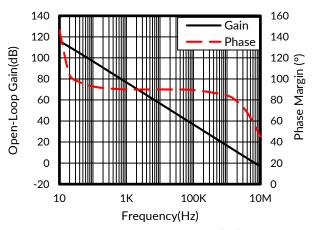

| FREQUE                                                                     | NCY RESPONSE                    |                                      |      |                    |        |                    |        |  |  |

| SR                                                                         | Slew Rate (8)                   |                                      | 25°C |                    | 3.7    |                    | V/µs   |  |  |

| GBP                                                                        | Gain-Bandwidth Product          |                                      | 25°C |                    | 7      |                    | MHz    |  |  |

| PM                                                                         | Phase Margin                    |                                      | 25°C |                    | 64     |                    | 0      |  |  |

| ts                                                                         | Settling Time, 0.1%             |                                      | 25°C |                    | 0.5    |                    | μs     |  |  |

| tor                                                                        | Overload recovery time          | V <sub>IN</sub> ×Gain≥V <sub>S</sub> | 25°C |                    | 0.5    |                    | μs     |  |  |

| NOISE                                                                      |                                 |                                      |      |                    |        |                    |        |  |  |

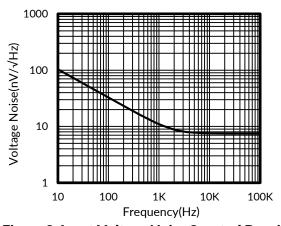

| _                                                                          | Input Voltage Noise Density     | f = 1KHz                             | 25°C |                    | 11     |                    | nV/√H: |  |  |

| e <sub>n</sub>                                                             | Input Voltage Noise Density     | f = 10KHz                            | 25°C |                    | 7.5    |                    | nV/√H: |  |  |

- (1) Electrical table values apply only for factory testing conditions at the temperature indicated. Factory testing conditions result in very limited self-heating of the device.

- (2) Limits are 100% production tested at 25°C. Limits over the operating temperature range are ensured through correlations using statistical quality control (SQC) method.

- (3) Typical values represent the most likely parametric norm as determined at the time of characterization. Actual typical values may vary over time and will also depend on the application and configuration.

- (4) This parameter is ensured by design and/or characterization and is not tested in production.

- (5) Positive current corresponds to current flowing into the device.

- (6) The maximum power dissipation is a function of  $T_{J(MAX)}$ ,  $R_{\theta JA}$ , and  $T_A$ . The maximum allowable power dissipation at any ambient temperature is  $P_D = (T_{J(MAX)} T_A) / R_{\theta JA}$ . All numbers apply for packages soldered directly onto a PCB.

- (7) Short circuit test is a momentary test.

- (8) Number specified is the slower of positive and negative slew rates.

- (9) Specified by characterization only.

## 7.5 Typical Characteristics

NOTE: The graphs and tables provided following this note are a statistical summary based on a limited number of samples and are provided for informational purposes only.

At  $T_A = +25$ °C,  $V_S = 5V$ ,  $R_L = 10k\Omega$  connected to  $V_S/2$ ,  $V_{OUT} = V_S/2$ , unless otherwise noted.

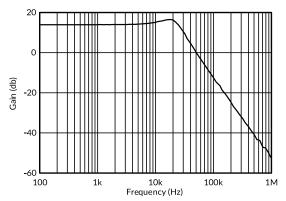

Figure 1. Open-Loop Gain And Phase vs Frequency

Figure 3. Common-Mode Rejection Ratio vs Frequency

Figure 5. Quiescent Current vs Temperature

Figure 2. Input Voltage Noise Spectral Density vs Frequency

Figure 4. Power-Supply Rejection Ratio vs Frequency

**Figure 6. Quiescent Current vs Temperature**

## **Typical Characteristics**

NOTE: The graphs and tables provided following this note are a statistical summary based on a limited number of samples and are provided for informational purposes only.

At  $T_A$  = +25°C,  $V_S$ =5V,  $R_L$  = 10k $\Omega$  connected to  $V_S$ /2,  $V_{OUT}$  =  $V_S$ /2, unless otherwise noted.

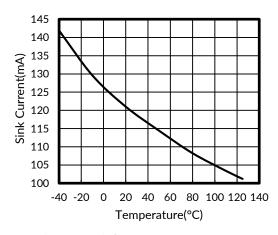

**Figure 7. Sink Current vs Temperature**

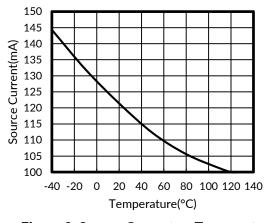

**Figure 8. Source Current vs Temperature**

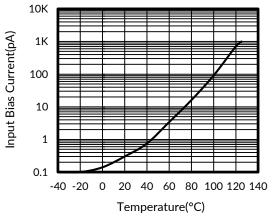

Figure 9. Input Bias Current vs Temperature

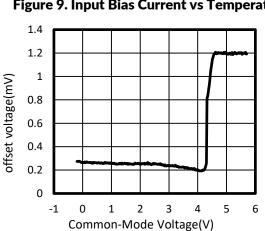

Figure 11. Offset Voltage vs Common-Mode Voltage

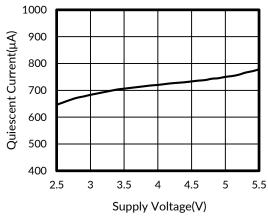

Figure 10. Quiescent Current vs Supply Voltage

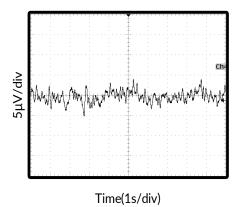

Figure 12. 0.1Hz To 10Hz Input Voltage Noise

## **Typical Characteristics**

NOTE: The graphs and tables provided following this note are a statistical summary based on a limited number of samples and are provided for informational purposes only.

At  $T_A$  = +25°C,  $V_S$ =5V,  $R_L$  = 10k $\Omega$  connected to  $V_S$ /2,  $V_{OUT}$  =  $V_S$ /2, unless otherwise noted.

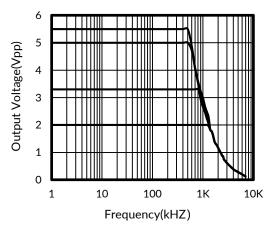

Figure 13. Maximum Output Voltage vs Frequency

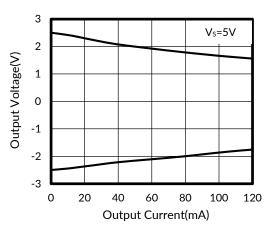

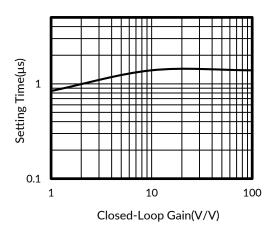

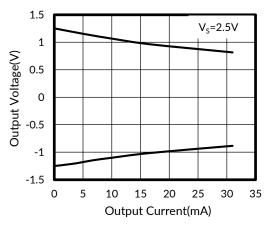

Figure 15. Output Voltage vs Output Current

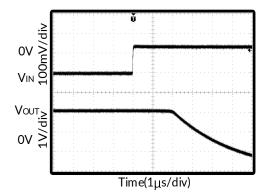

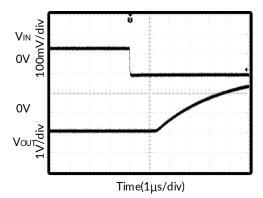

Figure 17. Positive Overload Recovery

Figure 14. Setting Time vs Closed-Loop Gain

Figure 16. Output Voltage vs Output Current

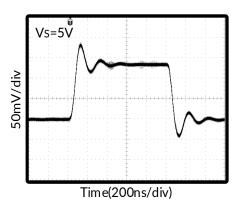

Figure 18. Negative Overload Recovery

## **Typical Characteristics**

NOTE: The graphs and tables provided following this note are a statistical summary based on a limited number of samples and are provided for informational purposes only.

At  $T_A$  = +25°C,  $V_S$ =5V,  $R_L$  = 10k $\Omega$  connected to  $V_S$ /2,  $V_{OUT}$  =  $V_S$ /2, unless otherwise noted.

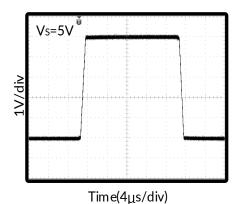

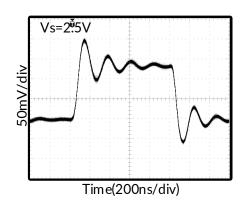

Figure 19. Small-Signal Step Response

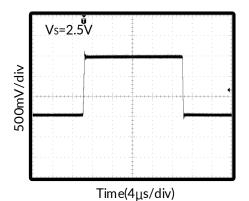

Figure 21. Large-Signal Step Response

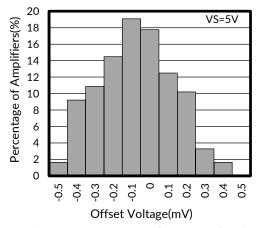

Figure 23. Offset Voltage Production Distribution

Figure 20. Small-Signal Step Response

Figure 22. Large-Signal Step Response

#### **8 DETAILED DESCRIPTION**

#### 8.1 Overview

The RS621K devices are unity-gain stable, dual and qual-channel op amps with low noise and distortion. The device consists of a low noise input stage with a folded cascade and a rail-to-rail output stage. This topology exhibits superior noise and distortion performance across a wide range of supply voltages that are not delivered by legacy commodity audio operational amplifiers.

#### 8.2 Phase Reversal Protection

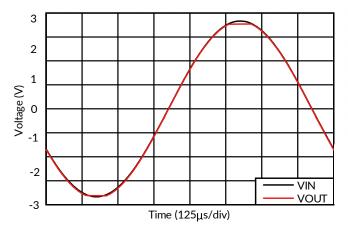

The RS621K family has internal phase-reversal protection. Many op amps exhibit phase reversal when the input is driven beyond the linear common-mode range. This condition is most often encountered in noninverting circuits when the input is driven beyond the specified common-mode voltage range, causing the output to reverse into the opposite rail. The input of the RS621K prevents phase reversal with excessive common-mode voltage. Instead, the appropriate rail limits the output voltage. This performance is shown in figure 24.

Figure 24. Output Waveform Devoid of Phase Reversal During an Input Overdrive Condition

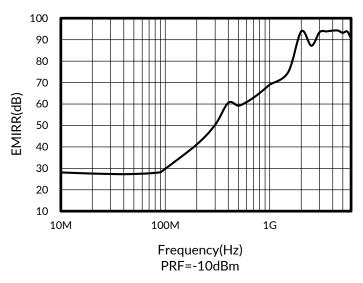

#### 8.3 EMI Rejection Ratio (EMIRR)

The electromagnetic interference (EMI) rejection ratio, or EMIRR, describes the EMI immunity of operational amplifiers. An adverse effect that is common to many operational amplifiers is a change in the offset voltage as a result of RF signal rectification. An operational amplifier that is more efficient at rejecting this change in offset as a result of EMI has a higher EMIRR and is quantified by a decibel value. Measuring EMIRR can be performed in many ways, but this document provides the EMIRR IN+, which specifically describes the EMIRR performance when the RF signal is applied to the noninverting input pin of the operational amplifier. In general, only the noninverting input is tested for EMIRR for the following three reasons:

- Operational amplifier input pins are known to be the most sensitive to EMI, and typically rectify RF signals better than the supply or output pins.

- The noninverting and inverting operational amplifier inputs have symmetrical physical layouts and exhibit nearly matching EMIRR performance.

- EMIRR is easier to measure on noninverting pins than on other pins because the noninverting input pin can

be isolated on a printed-circuit-board (PCB). This isolation allows the RF signal to be applied directly to the

noninverting input pin with no complex interactions from other components or connecting PCB traces.

## **DETAILED DESCRIPTION(continued)**

The EMIRR IN+ of the RS621K is plotted versus frequency in Figure 25. If available, any dual and quad operational amplifier device versions have approximately identical EMIRR IN+ performance. The RS621K unitygain bandwidth is 7MHz. EMIRR performance below this frequency denotes interfering signals that fall within the operational amplifier bandwidth.

Figure 25. RS621K EMIRR vs Frequency

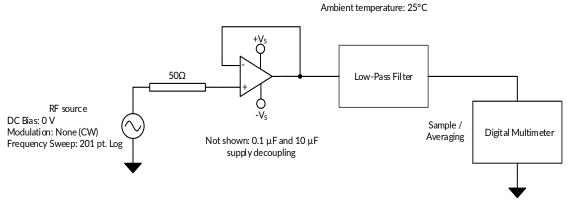

#### 8.4 EMIRR IN+ Test Configuration

Figure 26 shows the circuit configuration for testing the EMIRR IN+. An RF source is connected to the operational amplifier noninverting input pin using a transmission line. The operational amplifier is configured in a unity-gain buffer topology with the output connected to a low-pass filter (LPF) and a digital multimeter (DMM). A large impedance mismatch at the operational amplifier input causes a voltage reflection; however, this effect is characterized and accounted for when determining the EMIRR IN+. The resulting dc offset voltage is sampled and measured by the multimeter. The LPF isolates the multimeter from residual RF signals that can interfere with multimeter accuracy.

Figure 26. EMIRR IN+ Test Configuration Schematic

#### 9 APPLICATION AND IMPLEMENTATION

Information in the following applications sections is not part of the RUNIC component specification, and RUNIC does not warrant its accuracy or completeness. RUNIC's customers are responsible for determining suitability of components for their purposes. Customers should validate and test their design implementation to confirm system functionality.

#### 9.1 Application Note

The RS621K series features 7MHz bandwidth and  $3.7V/\mu s$  slew rate with only 700  $\mu A$  of supply current per channel, providing good AC performance at low power consumption. DC applications are well served with a low input noise voltage, low input bias current, and a typical input offset voltage of  $0.8 \, \text{mV}$ .

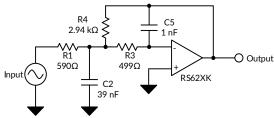

## Typical Applications 9.2 25-kHz Low-pass Filter

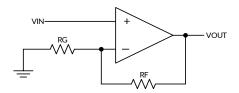

Figure 27. 25-kHz Low-Pass Filter

#### 9.3 Design Requirements

Low-pass filters are commonly employed in signal processing applications to reduce noise and prevent aliasing. The RS621K devices are ideally suited to construct high-speed, high-precision active filters. Figure 27 shows a second-order, low-pass filter commonly encountered in signal processing applications.

Use the following parameters for this design example:

- Gain = 5 V/V (inverting gain)

- Low-pass cutoff frequency = 25 kHz

- Second-order Chebyshev filter response with 3-dB gain peaking in the passband

#### 9.4 Detailed Design Procedure

The infinite-gain multiple-feedback circuit for a low-pass network function is shown in Figure 27. Use Equation 1 to calculate the voltage transfer function.

$$\frac{\text{Output}}{\text{Input}}(s) = \frac{-1/R_1R_3C_2C_5}{s^2 + (s/C_2) + (1/R_1 + 1/R_3 + 1/R_4) + 1/R_3R_4C_2C_5}$$

(1)

This circuit produces a signal inversion. For this circuit, the gain at dc and the low-pass cutoff frequency are calculated by Equation 2:

Gain =

$$\frac{R_4}{R_1}$$

$f_c = \frac{1}{2\pi} \sqrt{(1/R_3 R_4 C_2 C_5)}$  (2)

## 9.5 Application Curve

Figure 28. Low-Pass Filter Transfer Function

## **10 LAYOUT**

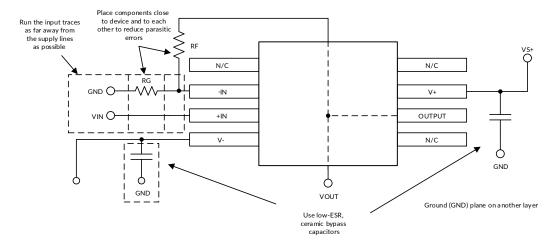

## 10.1 Layout Guideline

Attention to good layout practices is always recommended. Keep traces short. When possible, use a PCB ground plane with surface-mount components placed as close to the device pins as possible. Place a  $0.1\mu F$  capacitor closely across the supply pins.

These guidelines should be applied throughout the analog circuit to improve performance and provide benefits such as reducing the EMI susceptibility.

#### 10.2 Layout Example

Figure 29. Schematic Representation

Figure 30. Operational Amplifier Board Layout for Noninverting Configuration

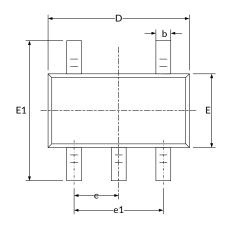

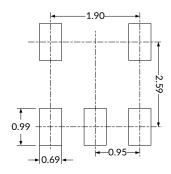

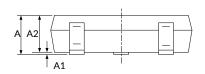

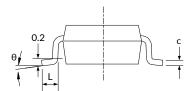

## 11 PACKAGE OUTLINE DIMENSIONS SOT23-5 (3)

RECOMMENDED LAND PATTERN (Unit: mm)

| Complete I | Dimensions I | n Millimeters | Dimension | s In Inches |

|------------|--------------|---------------|-----------|-------------|

| Symbol     | Min          | Max           | Min       | Max         |

| A (1)      | 1.050        | 1.250         | 0.041     | 0.049       |

| A1         | 0.000        | 0.100         | 0.000     | 0.004       |

| A2         | 1.050        | 1.150         | 0.041     | 0.045       |

| b          | 0.300        | 0.500         | 0.012     | 0.020       |

| С          | 0.100        | 0.200         | 0.004     | 0.008       |

| D (1)      | 2.820        | 3.020         | 0.111     | 0.119       |

| E (1)      | 1.500        | 1.700         | 0.059     | 0.067       |

| E1         | 2.650        | 2.950         | 0.104     | 0.116       |

| е          | 0.950(       | BSC) (2)      | 0.037(    | BSC) (2)    |

| e1         | 1.800        | 2.000         | 0.071     | 0.079       |

| L          | 0.300        | 0.600         | 0.012     | 0.024       |

| θ          | 0°           | 8°            | 0°        | 8°          |

- 1. Plastic or metal protrusions of 0.15mm maximum per side are not included.

- 2. BSC (Basic Spacing between Centers), "Basic" spacing is nominal.3. This drawing is subject to change without notice.

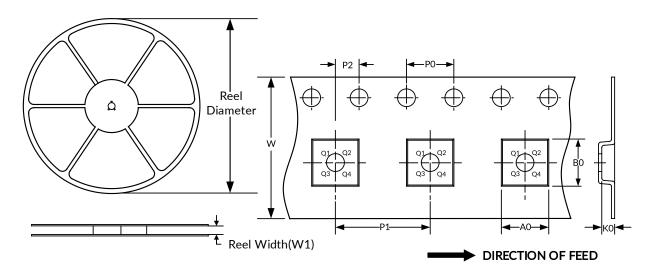

## 12 TAPE AND REEL INFORMATION REEL DIMENSIONS

#### **TAPE DIMENSION**

NOTE: The picture is only for reference. Please make the object as the standard.

## **KEY PARAMETER LIST OF TAPE AND REEL**

| Package Type | Reel<br>Diameter | Reel<br>Width(mm) | A0<br>(mm) | B0<br>(mm) | K0<br>(mm) | P0<br>(mm) | P1<br>(mm) | P2<br>(mm) | W<br>(mm) | Pin1<br>Quadrant |

|--------------|------------------|-------------------|------------|------------|------------|------------|------------|------------|-----------|------------------|

| SOT23-5      | 7"               | 9.5               | 3.20       | 3.20       | 1.40       | 4.0        | 4.0        | 2.0        | 8.0       | Q3               |

- 1. All dimensions are nominal.

- 2. Plastic or metal protrusions of 0.15mm maximum per side are not included.

#### IMPORTANT NOTICE AND DISCLAIMER

Jiangsu RUNIC Technology Co., Ltd. will accurately and reliably provide technical and reliability data (including data sheets), design resources (including reference designs), application or other design advice, WEB tools, safety information and other resources, without warranty of any defect, and will not make any express or implied warranty, including but not limited to the warranty of merchantability Implied warranty that it is suitable for a specific purpose or does not infringe the intellectual property rights of any third party.

These resources are intended for skilled developers designing with RUNIC products You will be solely responsible for: (1) Selecting the appropriate products for your application; (2) Designing, validating and testing your application; (3) Ensuring your application meets applicable standards and any other safety, security or other requirements; (4) RUNIC and the RUNIC logo are registered trademarks of RUNIC INCORPORATED. All trademarks are the property of their respective owners; (5) For change details, review the revision history included in any revised document. The resources are subject to change without notice. Our company will not be liable for the use of this product and the infringement of patents or third-party intellectual property rights due to its use.