# RS911xC 3.3-V and 2.5-V LVCMOS High-Performance Clock Buffer Family

#### 1 FEATURES

High-Performance 1:2, 1:3, 1:4 LVCMOS Clock Buffer Family

Supply Voltage: 3.3 V or 2.5 V

f<sub>max</sub> = 250 MHz for 3.3 V

f<sub>max</sub> = 180 MHz for 2.5 V

• Operating Temperature Range: -40°C to 85°C

• Available in 8-Pin TSSOP Package

#### **2 APPLICATIONS**

General-Purpose Communication, Industrial, and Consumer Applications

#### **3 DESCRIPTIONS**

Three different fan-out variations, 1:2 to 1:4, are available. All of the devices are pin-compatible to each other for easy handling.

All family members share the same high performing characteristics such as low skew, and wide operating temperature range.

The RS911xC supports an asynchronous output enable control (1G) which switches the outputs into a low state when 1G is low.

The RS911xC family operates in a 2.5-V and 3.3-V environment and are characterized for operation from -40°C to 85°C.

#### Device Information (1)

| PART NUMBER | PACKAGE | BODY SIZE (NOM)   |

|-------------|---------|-------------------|

| RS9112C     |         |                   |

| RS9113C     | TSSOP8  | 3.00 mm × 4.40 mm |

| RS9114C     |         |                   |

For all available packages, see the orderable addendum at the end of the data sheet.

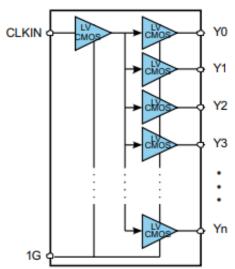

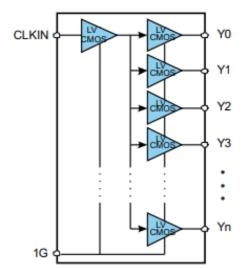

#### **4 Functional Block Diagram**

### **Table of Contents**

| 1 FEATURES                            | 1  |

|---------------------------------------|----|

| 2 APPLICATIONS                        | 1  |

| 3 DESCRIPTIONS                        | 1  |

| 4 Functional Block Diagram            | 1  |

| 5 Revision History                    | 3  |

| 6 Pin Configuration and Functions     | 4  |

| 7 SPECIFICATIONS                      | 5  |

| 7.1 Absolute Maximum Ratings          | 5  |

| 7.2 ESD Ratings                       | 5  |

| 7.3 Recommended Operating Conditions  | 5  |

| 7.4 Electrical Characteristics        | 6  |

| 7.5 Switching Characteristics         | 7  |

| 7.6 Parameter Measurement Information | 8  |

| 8 Detailed Description                | 10 |

| 8.1 Overview                          | 10 |

| 8.2 Functional Block Diagram          | 10 |

| 8.3 Feature Description               | 10 |

| 8.4 Device Functional Modes           | 10 |

| 9 Application and Implementation      | 11 |

| 9.1 Application Information           | 11 |

| 9.2 Typical Application               | 11 |

| 9.3 Design Requirements               | 11 |

| 9.4 Detailed Design Procedure         | 11 |

| 10 Power Supply Recommendations       | 12 |

| 10.1 Power Considerations             | 12 |

| 11 DACKACE OUTUNE DIMENSIONS          | 12 |

**5 Revision History**Note: Page numbers for previous revisions may different from page numbers in the current version.

| VERSION | Change Date | Change Item               |

|---------|-------------|---------------------------|

| A.1     | 2024/02/27  | Initial version completed |

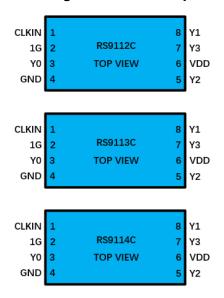

### **6 Pin Configuration and Functions**

#### **PW Package 8-Pin TSSOP Top View**

#### **Pin Functions**

|                    |            | PIN     |         |        | DECONOTION                    |  |  |  |  |

|--------------------|------------|---------|---------|--------|-------------------------------|--|--|--|--|

| NAME               | RS9112C    | RS9113C | RS9114C | TYPE   | DESCRIPTION                   |  |  |  |  |

| LVCMOS CLOCK INPUT |            |         |         |        |                               |  |  |  |  |

| CLKIN              | 1          | 1       | 1       | Input  | Input Pin                     |  |  |  |  |

| CLOCK OUT          | PUT ENABLE |         |         |        |                               |  |  |  |  |

| 1G                 | 2          | 2       | 2       | Input  | Output Enable                 |  |  |  |  |

| LVCMOS CL          | ОСК ОИТРИТ |         |         |        |                               |  |  |  |  |

| Y0                 | 3          | 3       | 3       |        |                               |  |  |  |  |

| Y1                 | _          | 8       | 8       | 0      | LVCMOS output. Unused outputs |  |  |  |  |

| Y2                 | _          | 5       | 5       | Output | can be left floating.         |  |  |  |  |

| Y3                 | _          | _       | 7       |        |                               |  |  |  |  |

| SUPPLY VO          | LTAGE      |         |         |        |                               |  |  |  |  |

| V <sub>DD</sub>    | 6          | 6       | 6       | Power  | 2.5-V or 3.3-Vdevice supply   |  |  |  |  |

| GROUND             | GROUND     |         |         |        |                               |  |  |  |  |

| GND                | 4          | 4       | 4       | GND    | Device ground                 |  |  |  |  |

#### **7 SPECIFICATIONS**

#### 7.1 Absolute Maximum Ratings

over operating free-air temperature range (unless otherwise noted) (1)

|                  |                              | MIN  | MAX                  | UNIT |

|------------------|------------------------------|------|----------------------|------|

| V <sub>DD</sub>  | Supply voltage               | -0.5 | 3.9                  | V    |

| V <sub>IN</sub>  | Input voltage <sup>(2)</sup> | -0.5 | V <sub>DD</sub> +0.5 | V    |

| Vo               | Output voltage (2)           | -0.5 | V <sub>DD</sub> +0.5 | V    |

| I <sub>IN</sub>  | input current                | -20  | 20                   | mA   |

| lo               | Continuous output current    | -50  | 50                   | mA   |

| TJ               | Maximum junction temperature |      | 125                  | °C   |

| T <sub>stg</sub> | Storage temperature          | -65  | 150                  | °C   |

<sup>(1)</sup> Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only and functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Conditions is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

#### 7.2 ESD Ratings

| 7 1 2 2 1 10 5 11 10 5 11 10 5 11 10 10 10 10 10 10 10 10 10 10 10 10 |                         |                                                                                |       |      |  |  |  |  |

|-----------------------------------------------------------------------|-------------------------|--------------------------------------------------------------------------------|-------|------|--|--|--|--|

|                                                                       |                         |                                                                                | VALUE | UNIT |  |  |  |  |

|                                                                       |                         | Human-body model (HBM), per ANSI/ESDA/JEDEC JS-001 <sup>(1)</sup>              | ±3000 |      |  |  |  |  |

| V <sub>(ESD)</sub>                                                    | Electrostatic discharge | Charged-device model (CDM), per JEDEC specification JESD22-C101 <sup>(2)</sup> | ±1500 | V    |  |  |  |  |

<sup>(1)</sup> JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

<sup>(2)</sup> JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process.

#### **ESD SENSITIVITY CAUTION**

ESD damage can range from subtle performance degradation to complete device failure. Precision integrated circuits may be more susceptible to damage because very small parametric changes could cause the device not to meet its published specifications.

#### 7.3 Recommended Operating Conditions

over operating free-air temperature range (unless otherwise noted)

|             |                                |                                            | MIN                      | NOM        | MAX                      | UNIT    |  |

|-------------|--------------------------------|--------------------------------------------|--------------------------|------------|--------------------------|---------|--|

| \/          | Supply voltage                 | 3.3V supply                                | 3                        | 3.3        | 3.6                      | V       |  |

| $V_{DD}$    |                                | 2.5V supply                                | 2.3                      | 2.5        | 2.7                      | ]       |  |

| VIL         | Low-level input voltage        | V <sub>DD</sub> = 3.0 V to 3.6 V           |                          |            | V <sub>DD</sub> /2 - 600 |         |  |

| VIL         |                                | $V_{DD}$ = 2.3 V to 2.7 V                  |                          |            | V <sub>DD</sub> /2 - 400 | mV      |  |

| \           | High-level input voltage       | $V_{DD}$ = 3.0 V to 3.6 V                  | V <sub>DD</sub> /2 + 600 |            |                          | \/      |  |

| VIH         |                                | $V_{DD}$ = 2.3 V to 2.7 V                  | V <sub>DD</sub> /2 + 400 |            |                          | mV      |  |

| $V_{TH}$    | Input threshold voltage        | V <sub>DD</sub> = 2.3 V to 3.6 V           |                          | $V_{DD}/2$ |                          | mV      |  |

| $t_r / t_f$ | Input slew rate                |                                            | 1                        |            | 4                        | V/ns    |  |

| _           | Minimum pulse width at         | $V_{DD} = 3.0 \text{ V to } 3.6 \text{ V}$ | 1.8                      |            |                          |         |  |

| tw          | CLKIN                          | $V_{DD}$ = 2.3 V to 2.7 V                  | 2.75                     |            |                          | ns      |  |

| £           | LVCMOS clock Input             | V <sub>DD</sub> = 3.0 V to 3.6 V           | DC                       |            | 250                      | N 41 1- |  |

| fclk        | Frequency                      | V <sub>DD</sub> = 2.3 V to 2.7 V           | DC                       |            | 180                      | MHz     |  |

| TA          | Operating free-air temperature |                                            | -40                      |            | 85                       | °C      |  |

<sup>(2)</sup> This value is limited to 3.9 V maximum.

#### 7.4 Electrical Characteristics

over operating free-air temperature range (unless otherwise noted)

|                  | PARAMETER                                    | TEST CONDITIONS                                                                                | MIN | <b>TYP</b> <sup>(1)</sup> | MAX | UNIT                                  |  |

|------------------|----------------------------------------------|------------------------------------------------------------------------------------------------|-----|---------------------------|-----|---------------------------------------|--|

| OVER             | ALL PARAMETERS FOR ALL VERSIO                | NS                                                                                             |     |                           |     |                                       |  |

|                  | Static device current                        | $1G = V_{DD}$ ; CLKIN = 0 V or $V_{DD}$ ; $I_O = 0$ mA; $V_{DD} = 3.6$ V                       |     | 3.5                       | 10  | - mA                                  |  |

| I <sub>DD</sub>  |                                              | $1G = V_{DD}$ ; CLKIN = 0 V or $V_{DD}$ ; $I_{O} = 0$ mA; $V_{DD} = 2.7$ V                     |     | 1.5                       | 6   |                                       |  |

| I <sub>PD</sub>  | Power-down current                           | $1G = 0 \text{ V}$ ; CLKIN = 0 V or $V_{DD}$ ; $I_0 = 0$ mA; $V_{DD} = 3.6 \text{ V}$ or 2.7 V |     | 34                        | 60  | μΑ                                    |  |

| _                | Power dissipation capacitance per            | V <sub>DD</sub> = 3.3 V; f = 10 MHz                                                            |     | 10.7                      |     | ,,F                                   |  |

| $C_{PD}$         | output <sup>(2)</sup>                        | V <sub>DD</sub> = 2.5 V; f = 10 MHz                                                            |     | 7.4                       |     | pF                                    |  |

|                  | Input leakage current at 1G                  | $V_{I} = 0 \text{ or } V_{DD}, V_{DD} = 3.6 \text{ Vor } 2.7 \text{ V}$                        |     | 10                        |     |                                       |  |

| lı               | Input leakage current at CLKIN               | $V_{I} = 0 \text{ or } V_{DD}, V_{DD} = 3.6 \text{ V or } 2.7 \text{ V}$                       |     | 28                        |     | μΑ                                    |  |

| _                | Output impedance                             | VDD = 3.3 V                                                                                    |     | 42                        |     |                                       |  |

| R <sub>OUT</sub> |                                              | VDD = 2.5 V                                                                                    |     | 49                        |     | Ω                                     |  |

| _                | Output frequency                             | VDD = 3 V to 3.6 V                                                                             | DC  |                           | 250 | MHz                                   |  |

| fout             |                                              | VDD = 2.3 V to 2.7 V                                                                           | DC  |                           | 180 |                                       |  |

| OUTF             | PUT PARAMETERS FOR V <sub>DD</sub> = 3.3 V ± | 0.3 V                                                                                          | •   | •                         | •   | •                                     |  |

|                  |                                              | V <sub>DD</sub> = 3 V, I <sub>OH</sub> = -0.1 mA                                               | 2.9 |                           |     |                                       |  |

| $V_{OH}$         | High-level output voltage                    | V <sub>DD</sub> = 3 V, I <sub>OH</sub> = -8 mA                                                 | 2.5 |                           |     | V                                     |  |

|                  |                                              | V <sub>DD</sub> = 3 V, I <sub>OH</sub> = -12 mA                                                | 2.2 |                           |     |                                       |  |

|                  |                                              | V <sub>DD</sub> = 3 V, I <sub>OL</sub> = 0.1 mA                                                |     |                           | 0.1 |                                       |  |

| $V_{\text{OL}}$  | Low-level output voltage                     | V <sub>DD</sub> = 3 V, I <sub>OL</sub> = 8 mA                                                  |     |                           | 0.5 | V                                     |  |

|                  |                                              | V <sub>DD</sub> = 3 V, I <sub>OL</sub> = 12 mA                                                 |     |                           | 0.8 |                                       |  |

| OUTF             | PUT PARAMETERS FOR V <sub>DD</sub> = 2.5 V ± | 0.2 V                                                                                          |     | •                         |     | •                                     |  |

| .,               |                                              | V <sub>DD</sub> = 2.3 V, I <sub>OH</sub> = -0.1 mA                                             | 2.2 |                           |     | .,,                                   |  |

| Vон              | High-level output voltage                    | V <sub>DD</sub> = 2.3 V, I <sub>OH</sub> = -8 mA                                               | 1.7 |                           |     | V                                     |  |

| \/               | 1 1 1 1 1                                    | V <sub>DD</sub> = 2.3 V, I <sub>OL</sub> = 0.1 mA                                              |     |                           | 0.1 | \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ |  |

| Vol              | Low-level output voltage                     | V <sub>DD</sub> = 2.3 V, I <sub>OL</sub> = 8 mA                                                |     |                           | 0.5 | V                                     |  |

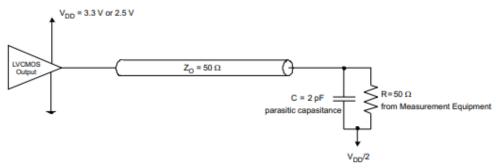

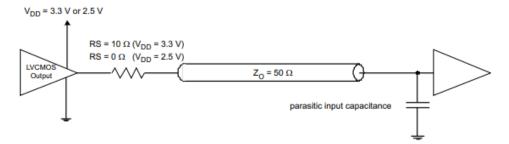

<sup>(1)</sup> All typical values are at respective nominal VDD. For switching characteristics, outputs are terminated to 50  $\Omega$  to  $V_{DD}/2$  (see Figure 1).

$$\begin{split} &P_{tot} = P_{stat} + P_{dyn} + P_{Cload}\left[W\right] \\ &P_{stat} = V_{DD} \times I_{DD}\left[W\right] \\ &P_{dyn} = C_{PD} \times V_{DD}^2 \times f\left[W\right] \\ &P_{Cload} = C_{load} \times V_{DD}^2 \times f \times n\left[W\right] \end{split}$$

n = Number of switching output pins

<sup>(2)</sup> This is the formula for the power dissipation calculation (see and the Power Considerations section).

### **7.5 Switching Characteristics** over operating free-air temperature range (unless otherwise noted)

|                                     | PARAMETER                                                    | TEST CONDITIONS                              | MIN | TYP (1) | MAX | UNIT |  |  |  |

|-------------------------------------|--------------------------------------------------------------|----------------------------------------------|-----|---------|-----|------|--|--|--|

| OUTPUT                              | OUTPUT PARAMETERS FOR VDD = 3.3 V ± 0.3 V                    |                                              |     |         |     |      |  |  |  |

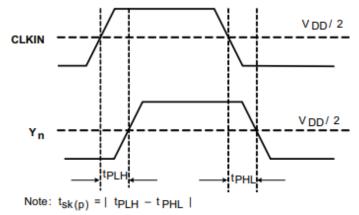

| t <sub>PLH</sub> / t <sub>PHL</sub> | Propagation delay                                            | CLKIN toYn                                   | 0.8 |         | 2.0 | ns   |  |  |  |

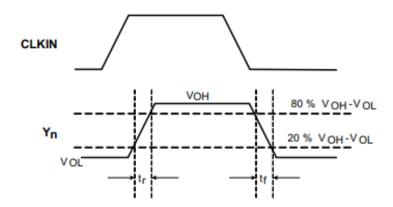

| t <sub>r</sub> / t <sub>f</sub>     | Rise and fall time                                           | 20%-80% (V <sub>OH</sub> - V <sub>OL</sub> ) | 0.3 |         | 0.8 | ns   |  |  |  |

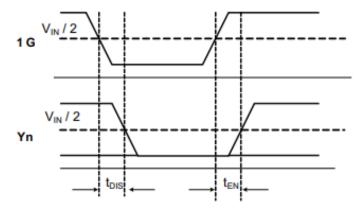

| t <sub>DIS</sub>                    | Output disable time                                          | 1G to Yn                                     |     |         | 6   | ns   |  |  |  |

| t <sub>EN</sub>                     | Output enable time                                           | 1G to Yn                                     |     |         | 6   | ns   |  |  |  |

| t <sub>sk(p)</sub>                  | Pulse skew ; t <sub>PLH(Yn)</sub> - t <sub>PHL(Yn)</sub> (1) |                                              |     |         | 180 | ps   |  |  |  |

| tjitter                             | Additive jitter rms <sup>(2)</sup>                           | 12 kHz to 20 MHz, fout = 250 MHz             |     |         | 100 | fs   |  |  |  |

| OUTPUT                              | PARAMETERS FOR V <sub>DD</sub> =2.5 \                        | / ± 0.2 V                                    |     |         |     |      |  |  |  |

| t <sub>PLH</sub> / t <sub>PHL</sub> | Propagation delay                                            | CLKIN to Yn                                  | 1   |         | 2.6 | ns   |  |  |  |

| t <sub>r</sub> / t <sub>f</sub>     | Rise and fall time                                           | 20%-80% (V <sub>OH</sub> - V <sub>OL</sub> ) | 0.3 |         | 1.2 | ns   |  |  |  |

| t <sub>DIS</sub>                    | Output disable time                                          | 1G to Yn                                     |     |         | 10  | ns   |  |  |  |

| t <sub>EN</sub>                     | Output enable time                                           | 1G to Yn                                     |     |         | 10  | ns   |  |  |  |

| t <sub>sk(p)</sub>                  | Pulse skew ; t <sub>PLH(Yn)</sub> – t <sub>PHL(Yn)</sub> (1) |                                              |     |         | 220 | ps   |  |  |  |

| tjitter                             | Additive jitter rms (2)                                      | 12 kHz to 20 MHz, fout = 180 MHz             |     |         | 350 | fs   |  |  |  |

<sup>(1)</sup>  $t_{sk(p)}$  depends on output rise- and fall-time  $(t_r/t_f)$ . The output duty-cycle can be calculated: odc =  $(t_{w(OUT)} \pm t_{sk(p)})/t_{period}$ ;  $t_{w(OUT)}$  is pulse-width of output waveform and  $t_{period}$  is  $1/t_{OUT}$ .

<sup>(2)</sup> Parameter is specified by characterization. Not tested in production

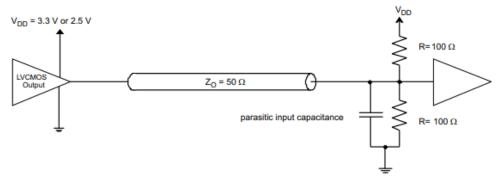

#### 7.6 Parameter Measurement Information

Figure 1. Test Load Circuit

Figure 2. Application Load With  $50-\Omega$  Line Termination

Figure 3. Application Load With Series Line Termination

Figure 4. t<sub>DIS</sub> and t<sub>EN</sub> for Disable Low

Figure 5. Pulse Skew tsk(p) and Propagation Delay  $t_{PLH}/t_{PHL}$

Figure 6. Rise/Fall Times  $t_r/t_f$

#### **8 Detailed Description**

#### 8.1 Overview

The RS911xC family of devices is a low-jitter and low-skew LVCMOS fan-out buffer solution. For best signal integrity, it is important to match the characteristic impedance of the RS911xC 's output driver with that of the transmission line. Figure 2 and Figure 3 show the proper configuration per configuration for both  $V_{DD}$  = 3.3 V and  $V_{DD}$  = 2.5 V. RUNIC recommends placing the series resistor close to the driver to minimize signal reflection.

#### 8.2 Functional Block Diagram

Figure 7. RS911xC functional block diagram

INPUTS

OUTPUTS

CLKIN

1G

Yn

X

L

L

L

L

L

H

H

H

**Table 1. Output Logic Table**

#### **8.3 Feature Description**

The outputs of the RS911xC can be disabled by driving the asynchronous output enable pin (1G) low. Unused output can be left floating to reduce overall system component cost. All supply and ground pins must be connected to  $V_{DD}$  and GND, respectively.

#### **8.4 Device Functional Modes**

The RS911xC operates from supplies between 2.5 V and 3.3 V.

#### 9 Application and Implementation

#### 9.1 Application Information

The RS911xC family is a low additive jitter LVCMOS buffer solution that can operate up to 250 MHz at and 180 MHz at  $V_{DD}$  = 2.5 V. Low output skew as well as the ability for asynchronous output enable is featured to simultaneously enable or disable buffered clock outputs as necessary in the application.

#### 9.2 Typical Application

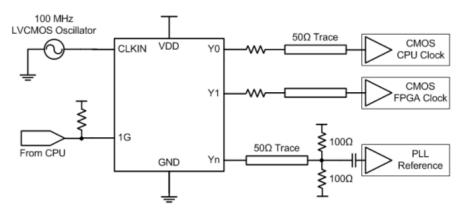

**Figure 8. Example System Configuration**

#### 9.3 Design Requirements

The RS911xC shown in Figure 8 is configured to fan out a 100-MHz signal from a local LVCMOS oscillator. The CPU is configured to control the output state through 1G. The configuration example is driving three LVCMOS receivers in a backplane application with the following properties:

- The CPU clock can accept a full swing DC-coupled LVCMOS signal. A series resistor is placed near the RS911xC to closely match the characteristic impedance of the trace to minimize reflections.

- The FPGA clock is similarly DC-coupled with an appropriate series resistor placed near the RS911xC.

- The PLL in this example can accept a lower amplitude signal, so a Thevenin's equivalent termination is used. The PLL receiver features internal biasing, so AC coupling can be used when common-mode voltage is mismatched.

#### 9.4 Detailed Design Procedure

Refer to Figure 3 and the Electrical Characteristics table to determine the appropriate series resistance needed for matching the output impedance of the RS911xC to that of the characteristic impedance of the transmission line.

Unused outputs can be left floating. See the Power Supply Recommendations section for recommended filtering techniques.

#### 10 Power Supply Recommendations

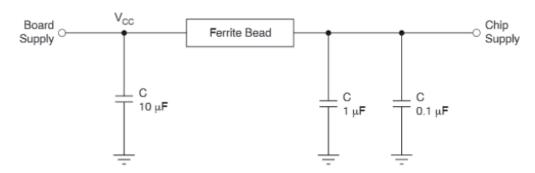

High-performance clock buffers are sensitive to noise on the power supply, which can dramatically increase the additive jitter of the buffer. Thus, it is essential to reduce noise from the system power supply, especially when the jitter and phase noise is critical to applications.

Filter capacitors are used to eliminate the low-frequency noise from the power supply, where the bypass capacitors provide the very low impedance path for high-frequency noise and guards the power supply system against induced fluctuations. These bypass capacitors also provide instantaneous current surges as required by the device and should have low equivalent series resistance (ESR). To properly use the bypass capacitors, they must be placed very close to the power-supply terminals and laid out with short loops to minimize inductance. RUNIC recommends adding as many high-frequency (for example,  $0.1~\mu\text{F}$ ) bypass capacitors, as there are supply terminals in the package. RUNIC recommends, but does not require, inserting a ferrite bead between the board power supply and the chip power supply that isolates the high-frequency switching noises generated by the clock buffer; these beads prevent the switching noise from leaking into the board supply. It is imperative to choose an appropriate ferrite bead with very low DC resistance to provide adequate isolation between the board supply and the chip supply, as well as to maintain a voltage at the supply terminals that is greater than the minimum voltage required for proper operation.

Figure 9 shows this recommended power supply decoupling method.

Figure 9. Power Supply Decoupling

#### **10.1 Power Considerations**

The following power consideration refers to the device-consumed power consumption only. The device power consumption is the sum of static power and dynamic power. The dynamic power usage consists of two components:

- Power used by the device as it switches states.

- Power required to charge any output load.

The output load can be capacitive only or capacitive and resistive. The following formula and the power graphs in and Figure 1 can be used to obtain the power consumption of the device:

```

\begin{split} P_{dev} &= P_{stat} + n \; (P_{dyn} + P_{Cload}) \\ P_{stat} &= V_{DD} \times I_{DD} \; P_{dyn} + P_{Cload} \end{split}

```

where:

$V_{DD}$  = Supply voltage ( 3.3Vor 2.5 V )

$I_{DD}$  = Static device current (typical 3.5 mA for  $V_{DD}$  = 3.3 V; typical 1.5 mA for  $V_{DD}$  = 2.5 V)

n = Number of switching output pins

Example for device power consumption for RS9114C: four outputs are switching, f = 120 MHz,  $V_{DD} = 3.3$  V, and  $C_{load} = 2$  pF per output:

12 / 13

```

P_{dev} = P_{stat} + n (P_{dyn} + P_{Cload}) = 11.55 \text{ mW} + 50 \text{ mW} = 61.55 \text{ mW}

```

$P_{stat} = V_{DD} \times I_{DD} = 3.5 \text{ mA} \times 3.3 \text{ V} = 11.55 \text{ mW}$

$n (P_{dyn} + P_{Cload}) = 4 \times 12.5 \text{ mW} = 50 \text{ mW}$

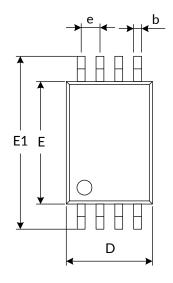

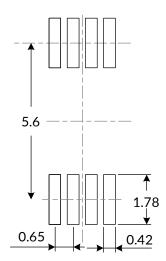

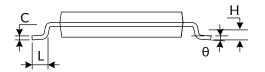

## 11 PACKAGE OUTLINE DIMENSIONS TSSOP8 (3)

**RECOMMENDED LAND PATTERN (Unit: mm)**

| Complete I | Dimensions I | Dimensions In Millimeters |           | s In Inches |

|------------|--------------|---------------------------|-----------|-------------|

| Symbol     | Min          | Мах                       | Min       | Max         |

| A (1)      |              | 1.200                     |           | 0.047       |

| A1         | 0.050        | 0.150                     | 0.002     | 0.006       |

| A2         | 0.800        | 1.050                     | 0.031     | 0.041       |

| b          | 0.190        | 0.300                     | 0.007     | 0.012       |

| С          | 0.090        | 0.200                     | 0.004     | 0.008       |

| D (1)      | 2.900        | 3.100                     | 0.114     | 0.122       |

| E (1)      | 4.300        | 4.500                     | 0.169     | 0.177       |

| E1         | 6.250        | 6.550                     | 0.246     | 0.258       |

| е          | 0.650(       | BSC) (2)                  | 0.026(    | BSC) (2)    |

| L          | 0.500        | 0.700                     | 0.020     | 0.028       |

| Н          | 0.25         | (TYP)                     | 0.01(TYP) |             |

| θ          | 1°           | 7°                        | 1°        | 7°          |

#### NOTE:

- 1. Plastic or metal protrusions of 0.15mm maximum per side are not included.

- 2. BSC (Basic Spacing between Centers), "Basic" spacing is nominal.

- 3. This drawing is subject to change without notice.